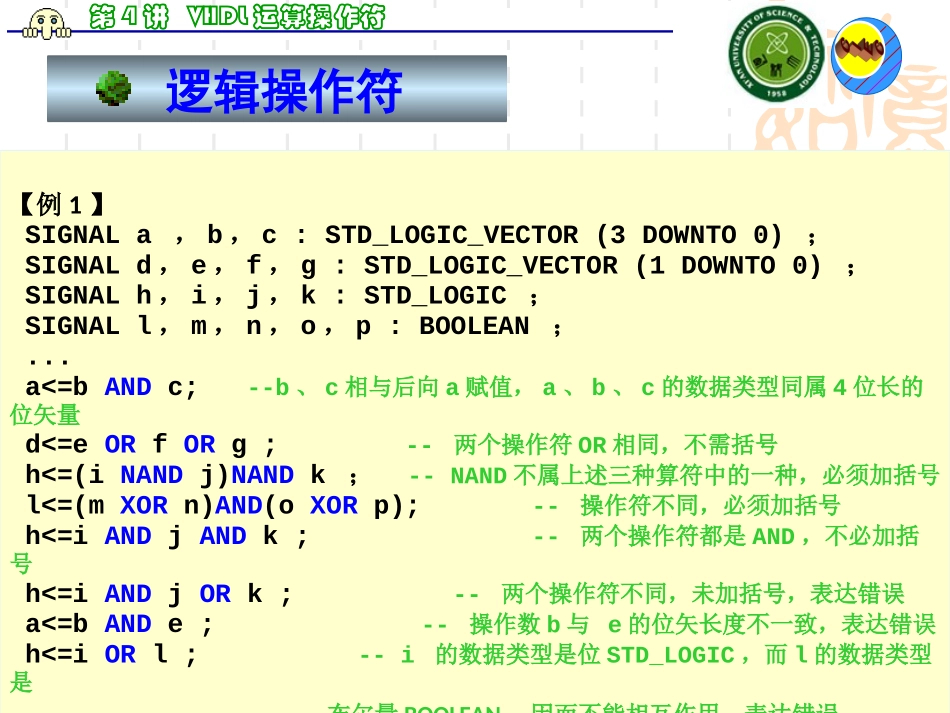

第4讲VHDL运算操作符赋值运算符逻辑运算符关系运算符算术运算符移位运算符并置运算符VHDL操作符与其他程序设计语言相似,VHDL中的表达式也是由运算符将基本元素连接起来形成。在VHDL语言中共有6类操作符第4讲VHDL运算操作符在VHDL语言中,共有6种逻辑运算符,他们分别是:NOT取反;AND与;OR或;NAND与非;NOR或非;XOR异或。逻辑运算符这6种逻辑运算符可以对“BIT”和“STD_LOGIC”等逻辑型数据、“STD_LOGIC_VECTOR”逻辑型数组及布尔数据进行逻辑运算。必须注意:运算符的左边和右边,以及代入的信号的数据类型必须是相同的。第4讲VHDL运算操作符【例1】SIGNALa,b,c:STD_LOGIC_VECTOR(3DOWNTO0);SIGNALd,e,f,g:STD_LOGIC_VECTOR(1DOWNTO0);SIGNALh,i,j,k:STD_LOGIC;SIGNALl,m,n,o,p:BOOLEAN;...a<=bANDc;--b、c相与后向a赋值,a、b、c的数据类型同属4位长的位矢量d<=eORfORg;--两个操作符OR相同,不需括号h<=(iNANDj)NANDk;--NAND不属上述三种算符中的一种,必须加括号l<=(mXORn)AND(oXORp);--操作符不同,必须加括号h<=iANDjANDk;--两个操作符都是AND,不必加括号h<=iANDjORk;--两个操作符不同,未加括号,表达错误a<=bANDe;--操作数b与e的位矢长度不一致,表达错误h<=iORl;--i的数据类型是位STD_LOGIC,而l的数据类型是...--布尔量BOOLEAN,因而不能相互作用,表达错误。逻辑操作符第4讲VHDL运算操作符关系操作符【例2】ENTITYrelational_ops_1ISPORT(a,b:INBIT_VECTOR(0TO3);output:OUTBOOLEAN);ENDrelational_ops_1;ARCHITECTUREexampleOFrelational_ops_1ISBEGINoutput<=(a=b);ENDexample;【例3】ENTITYrelational_ops_2ISPORT(a,b:ININTEGERRANGE0TO3;output:OUTBOOLEAN);ENDrelational_ops_2;ARCHITECTUREexampleOFrelational_ops_2ISBEGINoutput<=(a>=b);ENDexample;六种关系运算操作符:“=”(等于)、“/=”(不等于)、“>”(大于)、“<”(小于)、“>=”(大于等于)“<=”(小于等于)第4讲VHDL运算操作符VHDL语言中有5类算术运算符,他们分别是:求和操作符:+、-求积操作符:*、/、MOD、REM符号操作符:+、-混合操作符:**、ABS移位操作符:SLL、SRL、SLA、SRA、ROL、ROR算术运算符第4讲VHDL运算操作符求和操作符【例5】VARIABLEa,b,c,d,e,f:INTEGERRANGE0TO255;...a:=b+c;d:=e–f;【例4】PROCEDUREadding_e(a:ININTEGER;b:INOUTINTEGER)IS...b:=a+b;第4讲VHDL运算操作符【例6】PACKAGEexample_arithmeticISTYPEsmall_INtISRANGE0TO7;ENDexample_arithmetic;USEwork.example_arithmetic.ALL;ENTITYarithmeticISPORT(a,b:INSMALL_INT;c:OUTSMALL_INT);ENDarithmetic;ARCHITECTUREexampleOFarithmeticISBEGINc<=a+b;ENDexample;第4讲VHDL运算操作符求积操作符符号操作符求积操作符包括*(乘)、/(除)、MOD(取模)和REM(取余)四种操作符。符号操作符“+”和“-”的操作数只有一个。第4讲VHDL运算操作符混合操作符【例7】SIGNALa,b:INTEGERRANGE-8to7;SIGNALc:INTEGERRANGE0to15;SIGNALd:INTEGERRANGE0to3;a<=ABS(b);c<=2**d;“混合操作符包括乘方**”操作符和取“绝对值ABS”操作符两种第4讲VHDL运算操作符移位操作符移位操作符的语句格式是:标识符移位操作符移位位数;SLL(逻辑左移)SRL(逻辑右移)SLA(算术左移)SRA(算术右移)ROL(逻辑循环左移)ROR(逻辑循环右移)第4讲VHDL运算操作符【例8】LIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;USEIEEE.STD_LOGIC_UNSIGNED.ALL;ENTITYdecoder3to8ISport(input:INSTD_LOGIC_VECTOR(2DOWNTO0);output:OUTBIT_VECTOR(7DOWNTO0));ENDdecoder3to8;ARCHITECTUREbehaveOFdecoder3to8ISBEGINoutput<="00000001"SLLCONV_INTEGER(input);--被移位部分是常数!ENDbehave;第4讲VHDL运算操作符并置运算符SIGNALg,h,i:STD_LOGIC;SIGNALc,d,e:STD_LOGIC_VECTOR(1TO0);┇d<=i&NOTh;a<=c&d;元素与元素并置,形成长度为2的数组数组与数组并置,形成长度为4的数组&连接第4讲VHDL运算操作符赋值运算符赋值运算符用来给信号、变量和常量赋值。<=...