第五章时序逻辑电路102第五章时序逻辑电路教学目标、要求:掌握时序逻辑电路的概念;熟练掌握时序逻辑电路的分析与设计方法;熟练掌握计数器、寄存器和存储器的原理;掌握反馈归零、置数法构成N进制计数器;掌握RAM、ROM、PLD、CPLD的功能及使用方法;了解其电路结构和工作原理,了解FPLA的阵列结构与编程方法

内容提要:时序电路的基本分析与设计方法;计数器;寄存器和存储器;可编程逻辑器件

重点、难点:同步时序电路的一般分析方法;计数器的一般分析方法;;用集成计数器构成N进制计数器;寄存器的工作原理

教学方法:启发式、讨论式、探究时,理论、实验和实际应用有机结合

教学学时:12学时概述一、时序电路的特点组合逻辑电路基本单元是门电路,没有记忆功能;时序逻辑电路——电路任何一个时刻的输出状态不仅取决于当时的输入信号,还与电路的原状态有关

时序电路中必须含有具有记忆能力的存储器件

时序电路结构框图如图5

1时序逻辑电路结构方框图时序逻辑电路由组合电路和存储电路两部分构成

二、时序电路逻辑功能的表示方法时序电路的逻辑功能可用逻辑表达式、状态表、卡诺图、状态图、时序图和逻辑图6种方式表示,这些表示方法在本质上是相同的,可以互相转换

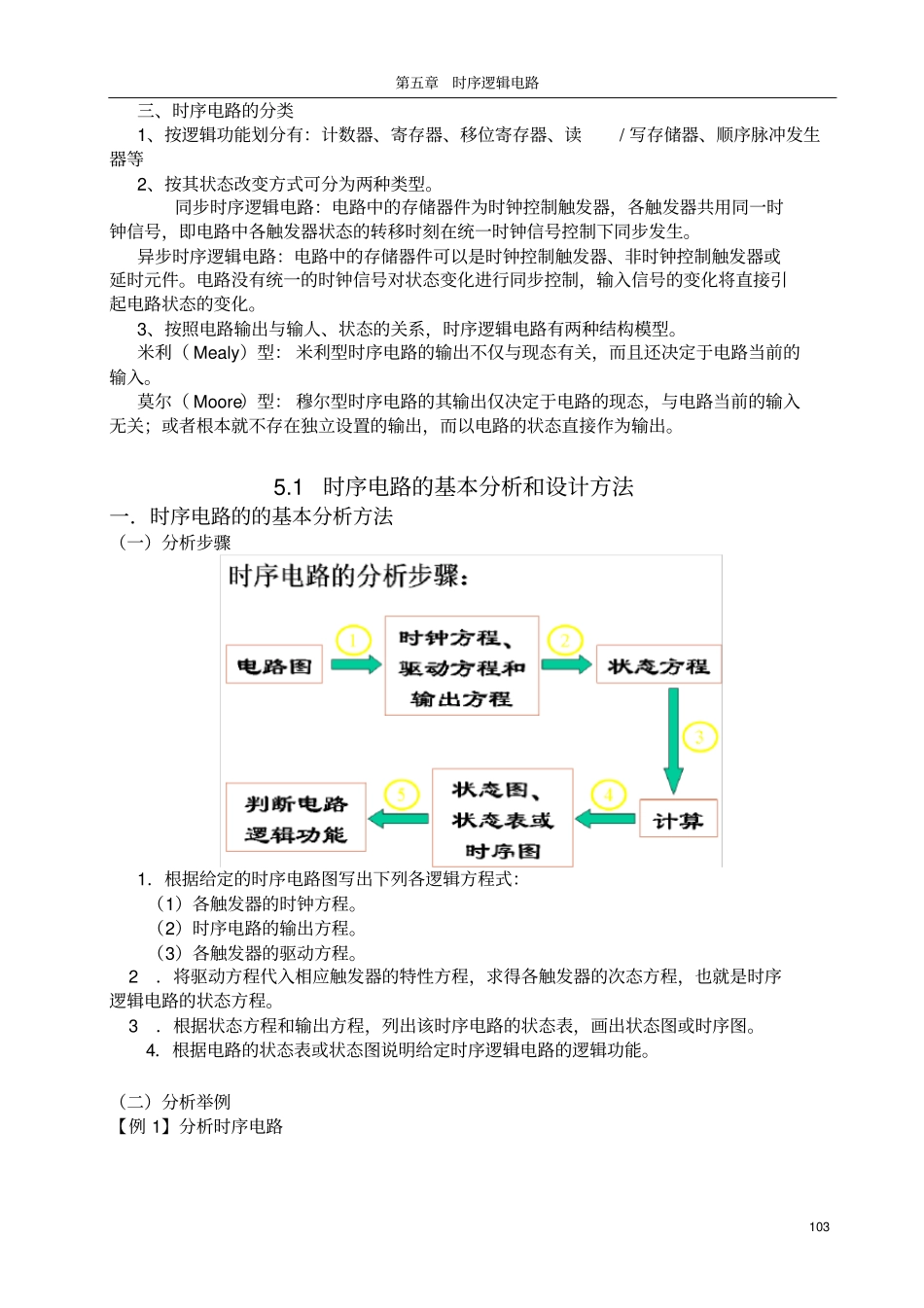

tkQQQWWWHQrjQQQXXXGWmiQQQXXXFYnqnnrknknqnnpjjnqnnpii,,2,1),,,;,,,(,,2,1),,,;,,,(,,2,1),,,;,,,(2121121212121输出方程、激励方程、状态方程第五章时序逻辑电路103三、时序电路的分类1、按逻辑功能划分有:计数器、寄存器、移位寄存器、读/写存储器、顺序脉冲发生器等2、按其状态改变方式可分为两种类型

同步时序逻辑电路:电路中的存储器件为时钟控制触发器,各触发器共用同一时钟信号,即电路中各触发器状态的转移时刻在统一时钟信号控制下同步发生

异步时序逻辑电