1实验六用中规模组合逻辑器件设计组合逻辑电路一、实验目的1.学习中规模集成数据选择器的逻辑功能和使用方法

2.学习使用中规模集成芯片实现多功能组合逻辑电路的方法

二、设计任务用数据选择器74LS151或3/8线译码器设计一个多功能组合逻辑电路

该电路具有两个控制端C1C0,控制着电路的功能,当C1C0=00时,电路实现对输入的两个信号的或的功能;当C1C0=01时,电路实现对输入的两个信号的与的功能;当C1C0=10时,电路实现对输入的两个信号的异或的功能;当C1C0=11时,电路实现对输入的两个信号的同或的功能

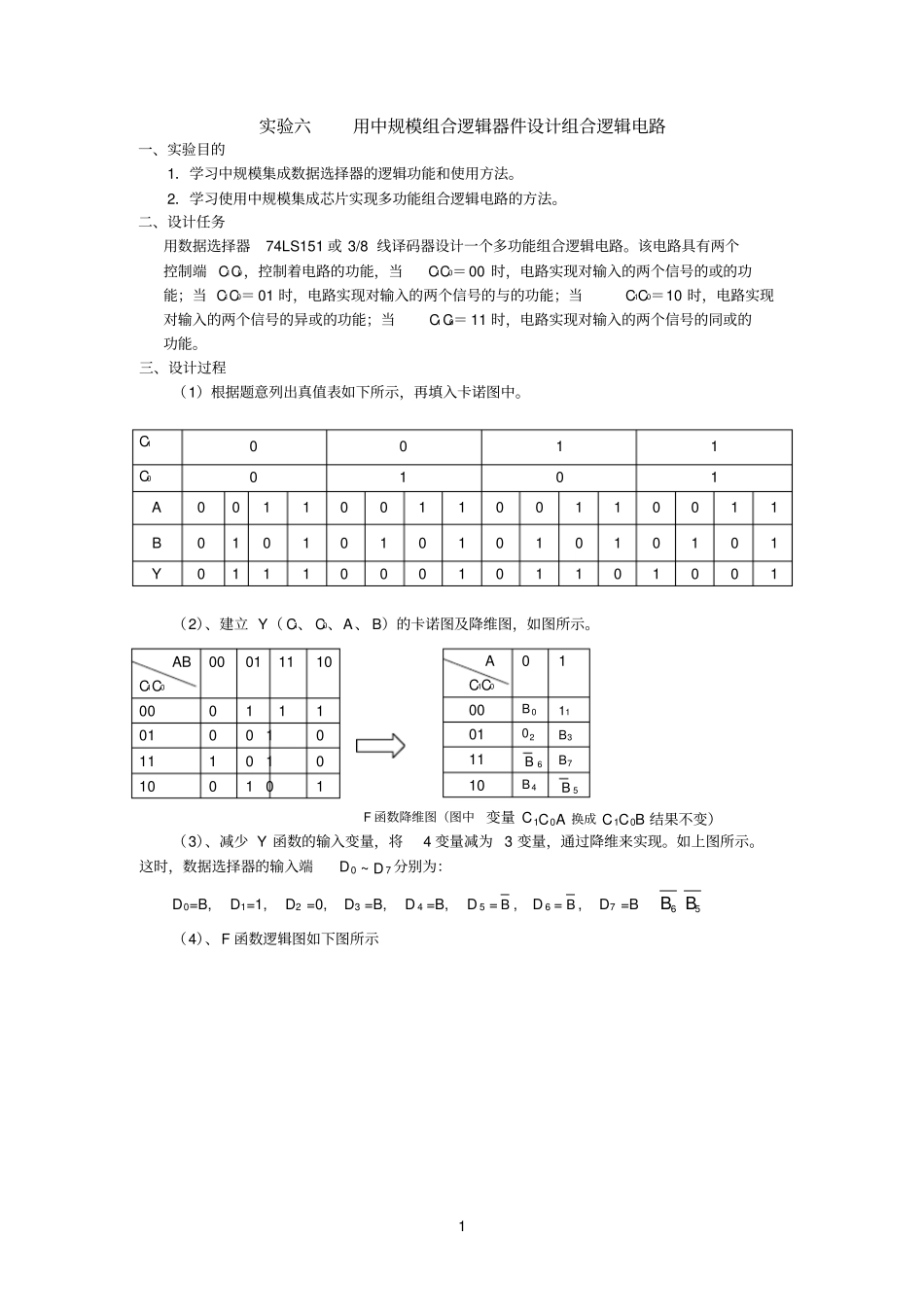

三、设计过程(1)根据题意列出真值表如下所示,再填入卡诺图中

C10011C00101A0011001100110011B0101010101010101Y0111000101101001(2)、建立Y(C1、C0、A、B)的卡诺图及降维图,如图所示

F函数降维图(图中变量C1C0A换成C1C0B结果不变)(3)、减少Y函数的输入变量,将4变量减为3变量,通过降维来实现

这时,数据选择器的输入端D0~D7分别为:D0=B,D1=1,D2=0,D3=B,D4=B,D5=B,D6=B,D7=B6B5B(4)、F函数逻辑图如下图所示ABC1C000011110000111010010111010100101AC1C00100B0110102B311B6B710B4B52四、实验用仪器、仪表数字电路实验箱、万用表、74LS151、74LS00

五、实验步骤1.检查导线及器件好坏

2.按上图连接电路

C1、C0、A、B分别接逻辑开关,检查无误后接通电源

3.按真值表逐项进行测试并检查是否正确,如有故障设法排除

4.结果无误后记录数据后拆线并整理实验设备

实验数据如下:C10011C00101A0011001100110011B0101010101010101Y0