1. 简介 这个文档介绍了 PCI Express 布线过程中要注意的事项

PCI Express 互连 PCI Express是一种双单工连接的点对点串行差分低电压互联

每个通道有两对差分信号:传输对 TXP/TXN,接收对RXP/RXN

该信号工作在 2

5 GHz并带有嵌入式时钟

嵌入式时钟通过消除不同差分对的长度匹配简化了布线规则

不断增加的PCI Express比特率需要一些特别的设计

而其中最小化互连损耗和抖动预算是关键要求

1 PCI Express 的PCB 叠层和参考面 在PCI Express并没有使用新技术

一般的PC主板设计成 4层叠层,而服务器,工作站和移动系统主板多使用 6层或是更多层的叠层

插卡可以使用 4层或是 6层叠层

5OZ的镀铜微带线和1OZ的铜带状线

插卡的整体电路板的厚度必须是 0

062inch

移动平台的PCB厚度可以是 0

062inch或是 0

050inch

为了尽可能的减少损耗和抖动预算,最重要的考虑因素是设计的目标阻抗,而且要保持阻抗的公差足够小

更厚的介质层和更宽的走线将会减少损耗

微带差分线会比带状差分线产生更大的阻抗变化

信号对应避免参考平面的不连续,譬如分割和空隙

当信号线变化层时,地信号的过孔应放得靠近信号过孔

对每对信号的建议是至少放 1到 3个地信号过孔

还有永远不要让走线跨过平面的分割

2 走线 2

1 阻抗 PCI Express 的连接走线阻抗在 4 层或 6 层板时必须保持 100Ω 差分/60Ω单端;而对 8 层或 10 层板阻抗为 85 Ω 差分/ 55 Ω 单端

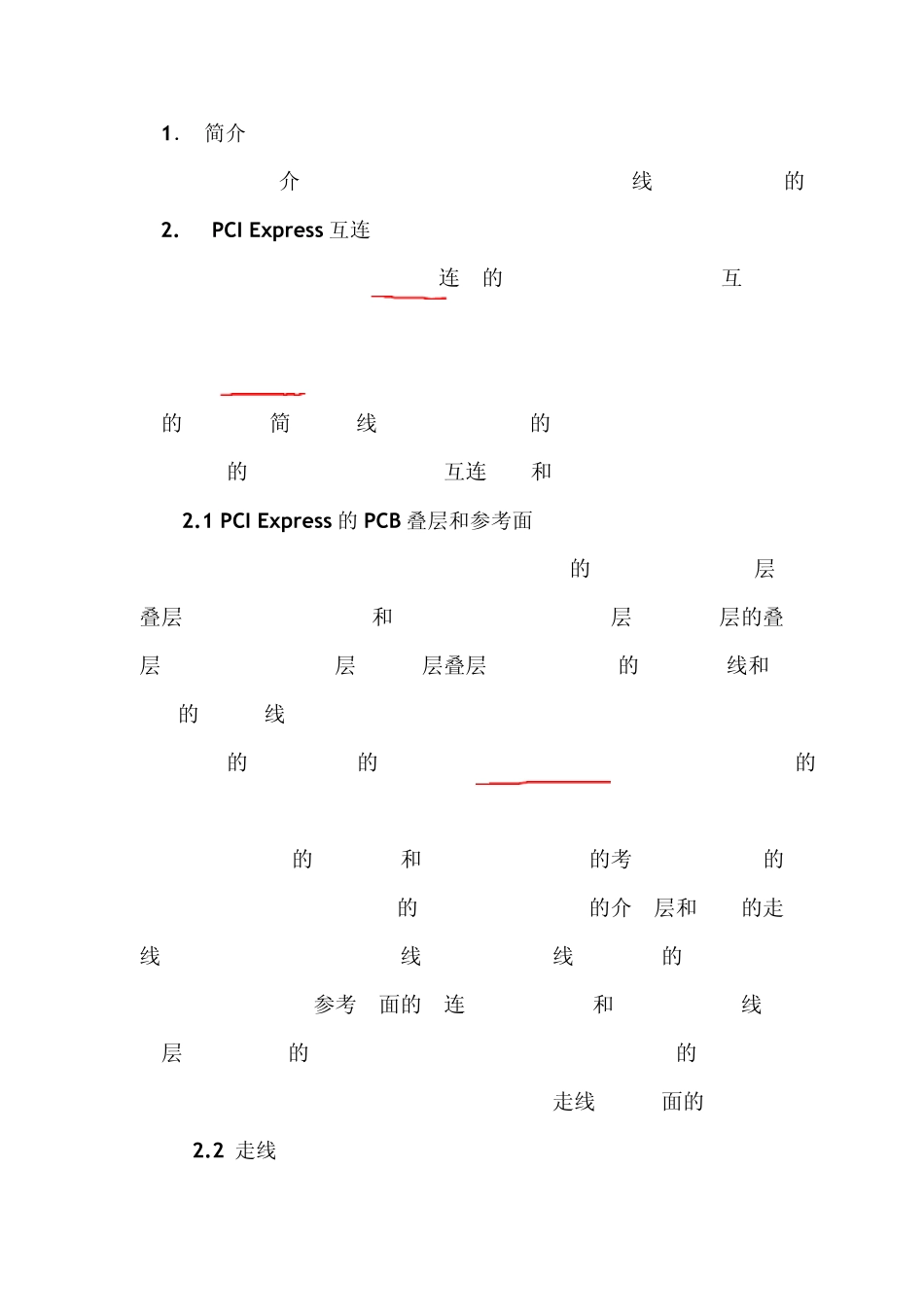

2 线宽和线距 差分信号的内部耦合和增加与周边的信号间距有助于减少有害串扰的影响和电磁干扰(EMI)的影响

在微带情况下,差分线的宽度是 5 mil,差分对中的2条走线的间距