SDRAM 时钟相移估算 《Qu artu s II Handbook Version 9

0 Volu me 5:Embedded Peripherals》中Section I 的1

SDRAM Controller Core 部分提出了如何估计SDRAM 数据有效信号窗口,并且给出了SDRAM 时钟相对于FPGA 时钟相移估计公式

下面先就事论事,对官方给出的这个公式做一些推导说明

(详细的内容请读者参考上面给出的资料,本文重点讨论估算公式

)原文的四个公式如图 1和图 2 所示

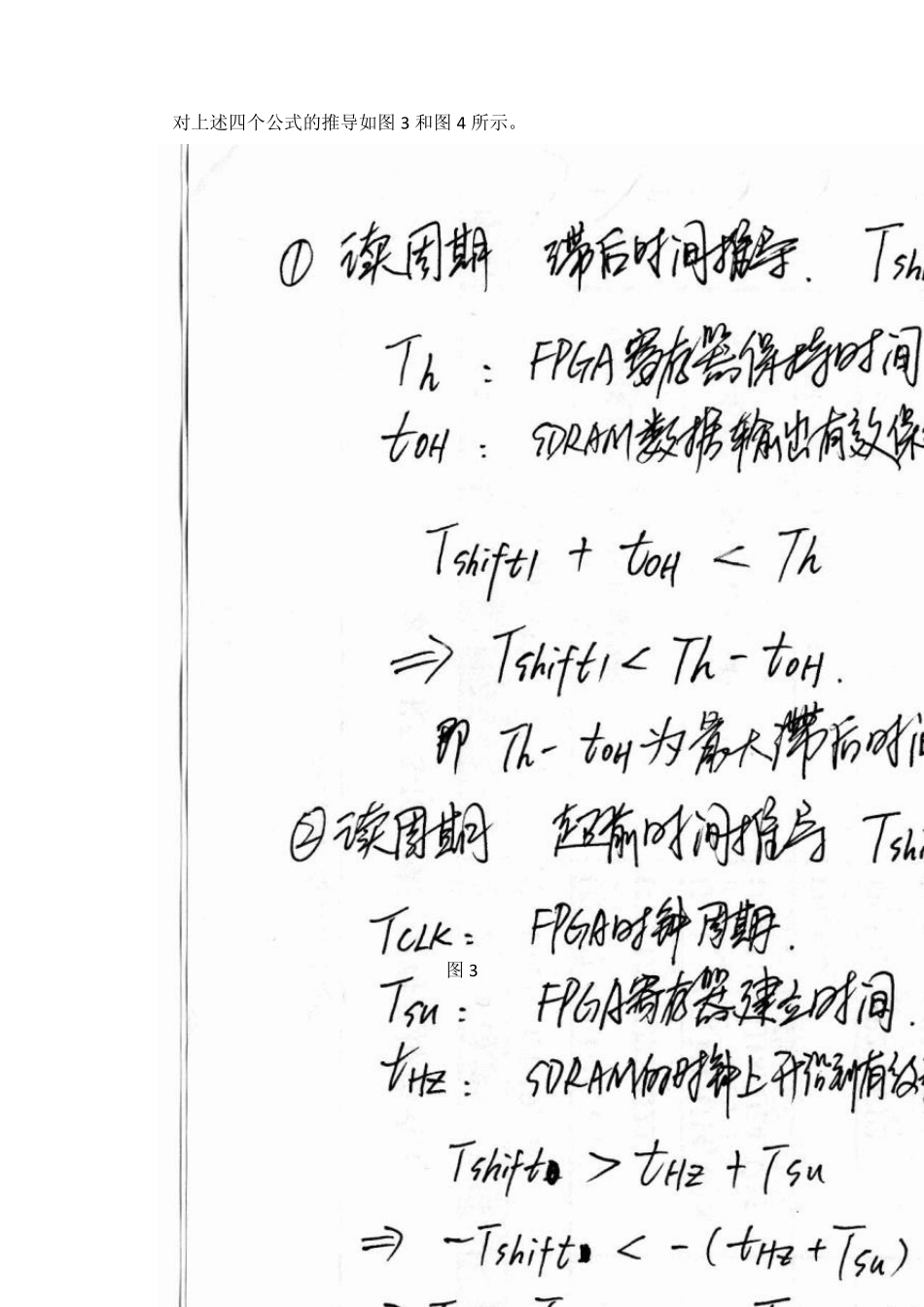

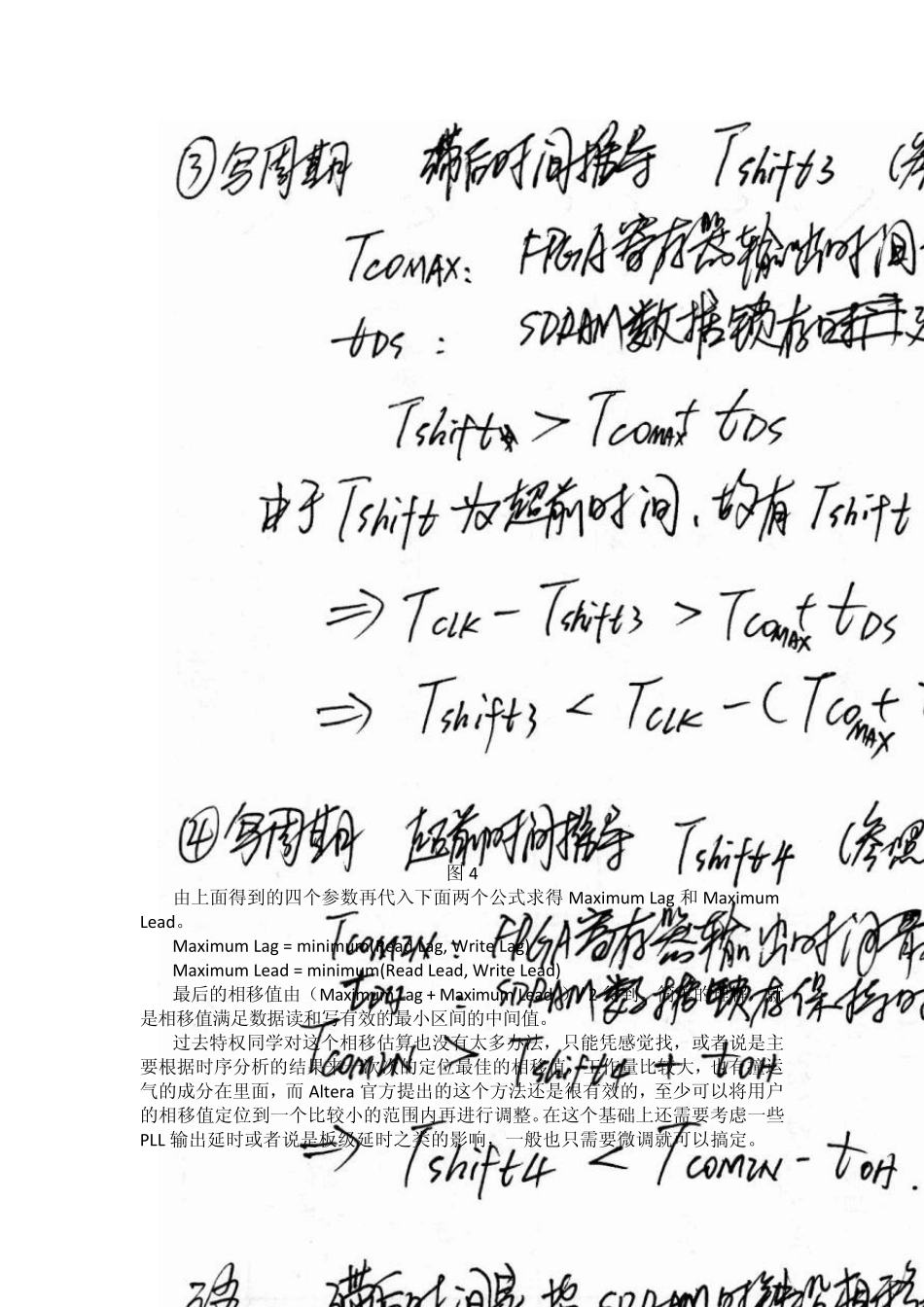

图 1 图 2 对上述四个公式的推导如图3 和图4 所示

图3 图4 由上面得到的四个参数再代入下面两个公式求得Maximum Lag 和Maximum Lead

Maximum Lag = minimum(Read Lag, Write Lag) Maximum Lead = minimum(Read Lead, Write Lead) 最后的相移值由(Maximum Lag + Maximum Lead )/ 2 得到

简单的理解,就是相移值满足数据读和写有效的最小区间的中间值

过去特权同学对这个相移估算也没有太多办法,只能凭感觉找,或者说是主要根据时序分析的结果来一次次的定位最佳的相移值,工作量比较大,也有撞运气的成分在里面,而 Altera 官方提出的这个方法还是很有效的,至少可以将用户的相移值定位到一个比较小的范围内再进行调整

在这个基础上还需要考虑一些PLL 输出延时或者说是板级延时之类的影响,一般也只需要微调就可以搞定

为了验证这种估算方法在工程应用中是否可行,特权同学特地拿出过去一个比较稳定工作的SDRAM 控制器的一些参数进行计算

估算需要涉及到的参数如图5、图6、图7、图8 所示

图5 是slack 最小的R2P 输出时间;图6 是slack最大的R2P 输出