Simulation and Synthesis Techniques for Asynchronous FIFO Design with Asynchronous Pointer Comparisons Clifford E

Cummings Peter Alfke Sunburst Design, Inc

Xilinx, Inc

SNUG-2002 San Jose, CA Voted Best Paper 1st Place ABSTRACT An interesting technique for doing FIFO design is to perform asynchronous comparisons between the FIFO write and read pointers that are generated in clock domains that are asynchronous to each other

The asynchronous FIFO pointer comparison technique uses fewer synchronization flip-flops to build the FIFO

The asynchronous FIFO comparison method requires additional techniques to correctly synthesize and analyze the design, which are detailed in this paper

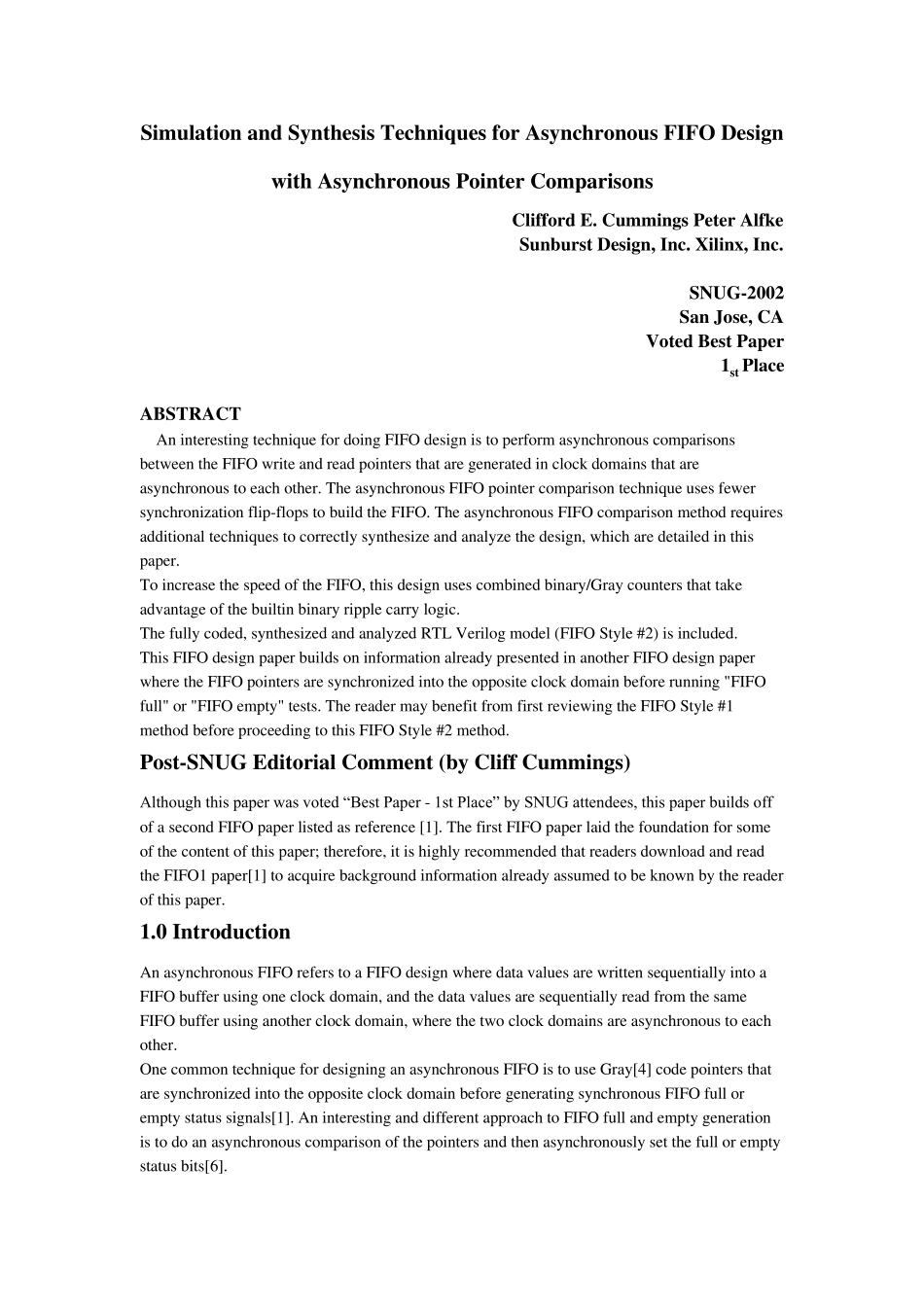

To increase the speed of the FIFO, this design uses combined binary/Gray counters that take advantage of the