西北工业大学 《FPGA 技术实验》 实验报告四 (四位秒表的设计与实现) 学 院: 软件与微电子学院 学 号: 姓 名: 专 业: 微电子学 实验时间: 2011

16 实验地点: 毅字楼 335 指导教师: *** 西北工业大学 2011 年 11 月 一、实验目的及要求 实验目的:学会复杂编程的思想,综合运用 verilog 语言,进行复杂电路设计及根据模拟综合仿真结果对设计进行优化

实验要求:设计时长度为 1 小时,计时精度为 1 秒;初始值为:00:00 计时最大值:59:59

按照三个模块进行,顶层模块不做逻辑设计,只对底层模块例化,底层模块分为计时模块和译码模块

二、实验设备(环境)及要求 本次实验使用的主要工具为:Synplify Pro 9

2 和 ModelSim SE 6

三、实验内容与步骤 1

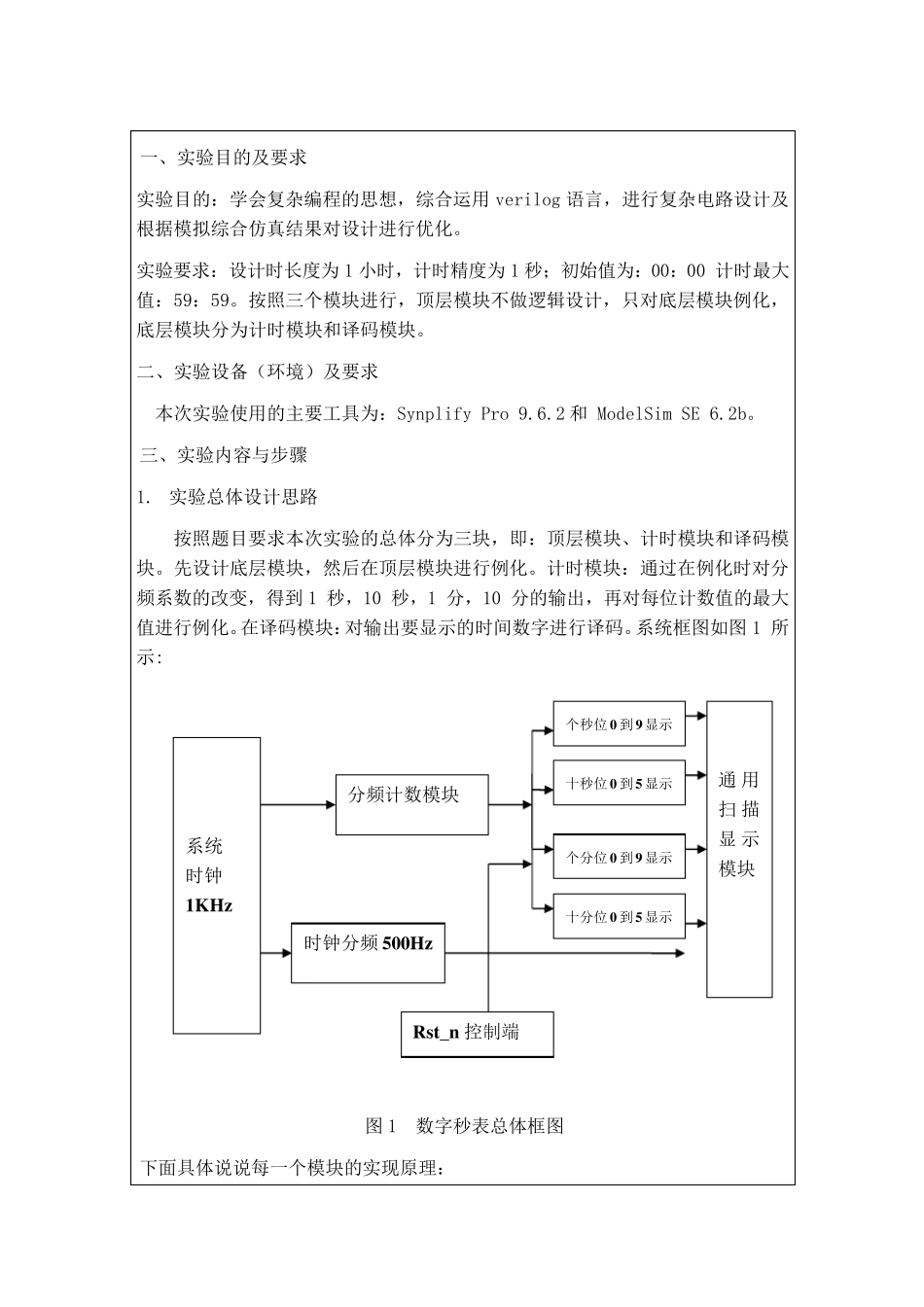

实验总体设计思路 按照题目要求本次实验的总体分为三块,即:顶层模块、计时模块和译码模块

先设计底层模块,然后在顶层模块进行例化

计时模块:通过在例化时对分频系数的改变,得到 1 秒,10 秒,1 分,10 分的输出,再对每位计数值的最大值进行例化

在译码模块:对输出要显示的时间数字进行译码

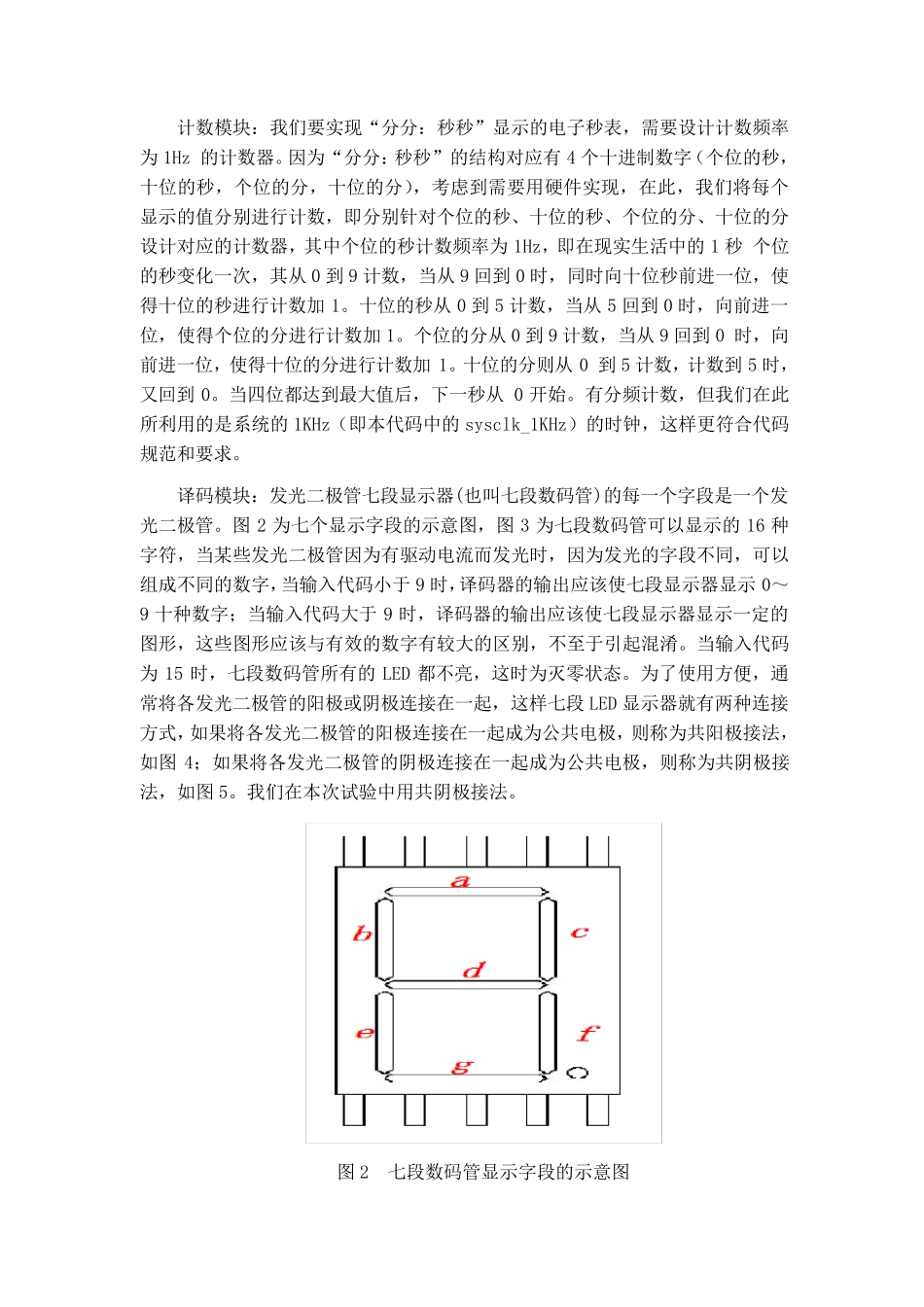

系统框图如图 1 所示: 图 1 数字秒表总体框图 下面具体说说每一个模块的实现原理: 分频计数模块 时钟分频 500Hz 通 用扫 描显 示模块 个秒位 0 到 9 显示 十秒位 0 到 5 显示 个分位 0 到 9 显示 十分位 0 到 5 显示 Rst_n 控制端 系统 时钟 1KHz 计数模块:我们要实现“分分:秒秒”显示的电子秒表,需要设计计数频率为 1Hz 的计数器

因为“分分:秒秒”的结构对应有 4 个十进制数字(个位的秒,十位的秒,个位的分,十位的分),考虑到需要用硬件实现,在此,我们将每个显示的值分别进行计数,即分别针对个位的秒、十