基于Verilog 的VGA 驱动设计(一)VGA 时序分析 VGA 时序分析 电阻DAC 转换网络和640X480 的VGA 时序图: 图1 扫描频率 显示器采用光栅扫描方式,即轰击荧光屏的电子束在CRT 屏幕上从左到右(受水平同步信号HSYNC 控制)、从上到下(受垂直同步信号VSYNC 控制)做有规律的移动

光栅扫描又分逐行扫描和隔行扫描

电子束采用光栅扫描方式,从屏幕左上角一点开始,向右逐点进行扫描,形成一条水平线;到达最右端后,又回到下一条水平线的左端,重复上面的过程;当电子束完成右下角一点的扫描后,形成一帧

此后,电子束又回到左上方起点,开始下一帧的扫描

这种方法也就是常说的逐行扫描显示

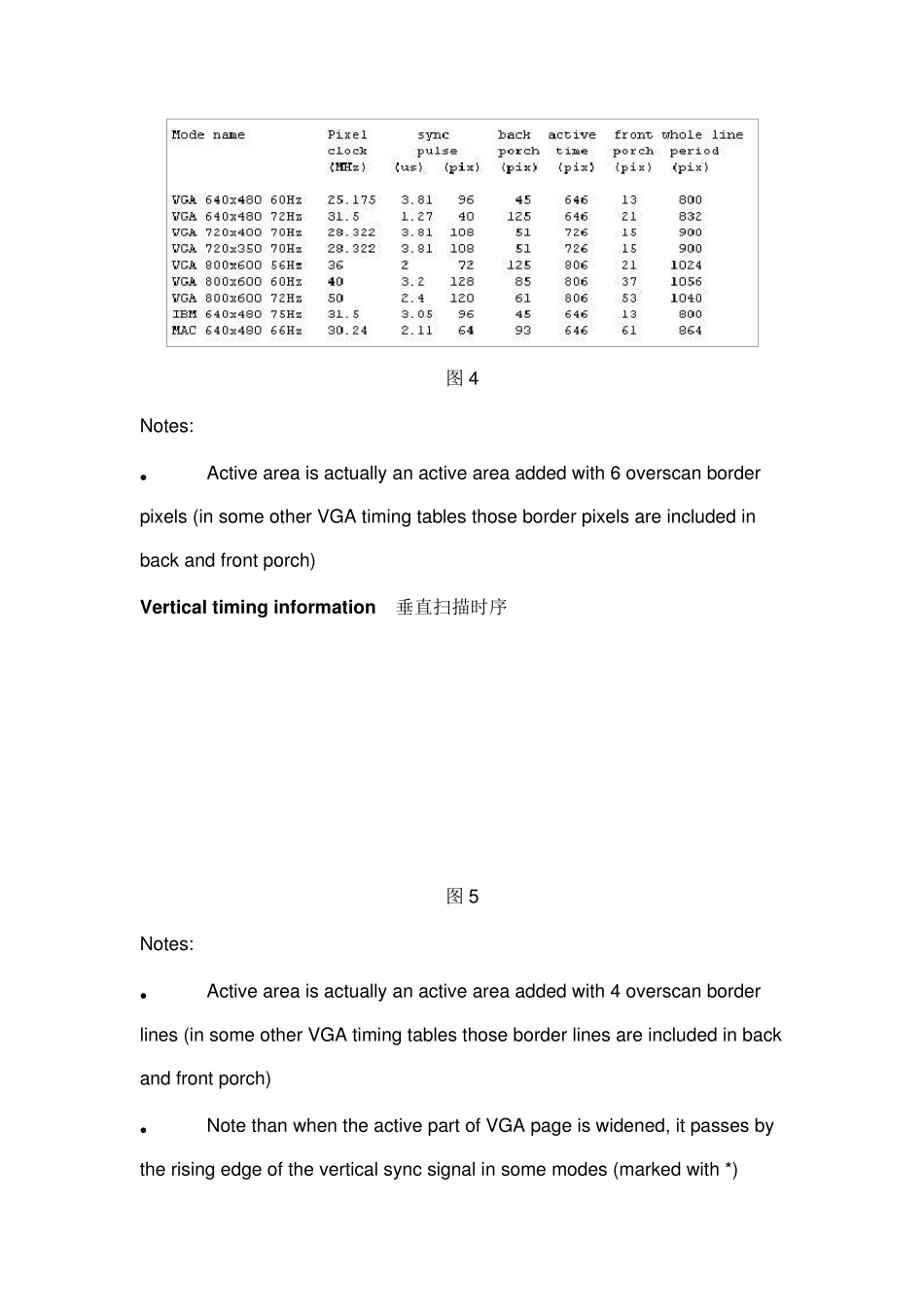

Horiz onal Timing 图2 A (us) Line Period(1040*20ns) B (us) Sync pulse lenght C (us) Back porch D (us) Active video time E (us) Front porch 2.Vertical Timing 图3 O (ms) Frame Period 帧周期 P (ms) Sync length Q (ms) Back porch R (ms) Active video time S (ms) Front porch Horiz onal timing information 水平扫描时序 图 4 Notes: • Active area is actually an active area added with 6 overscan border pixels (in some other VGA timing tables those border pixels are included in back and front porch) Vertical timi