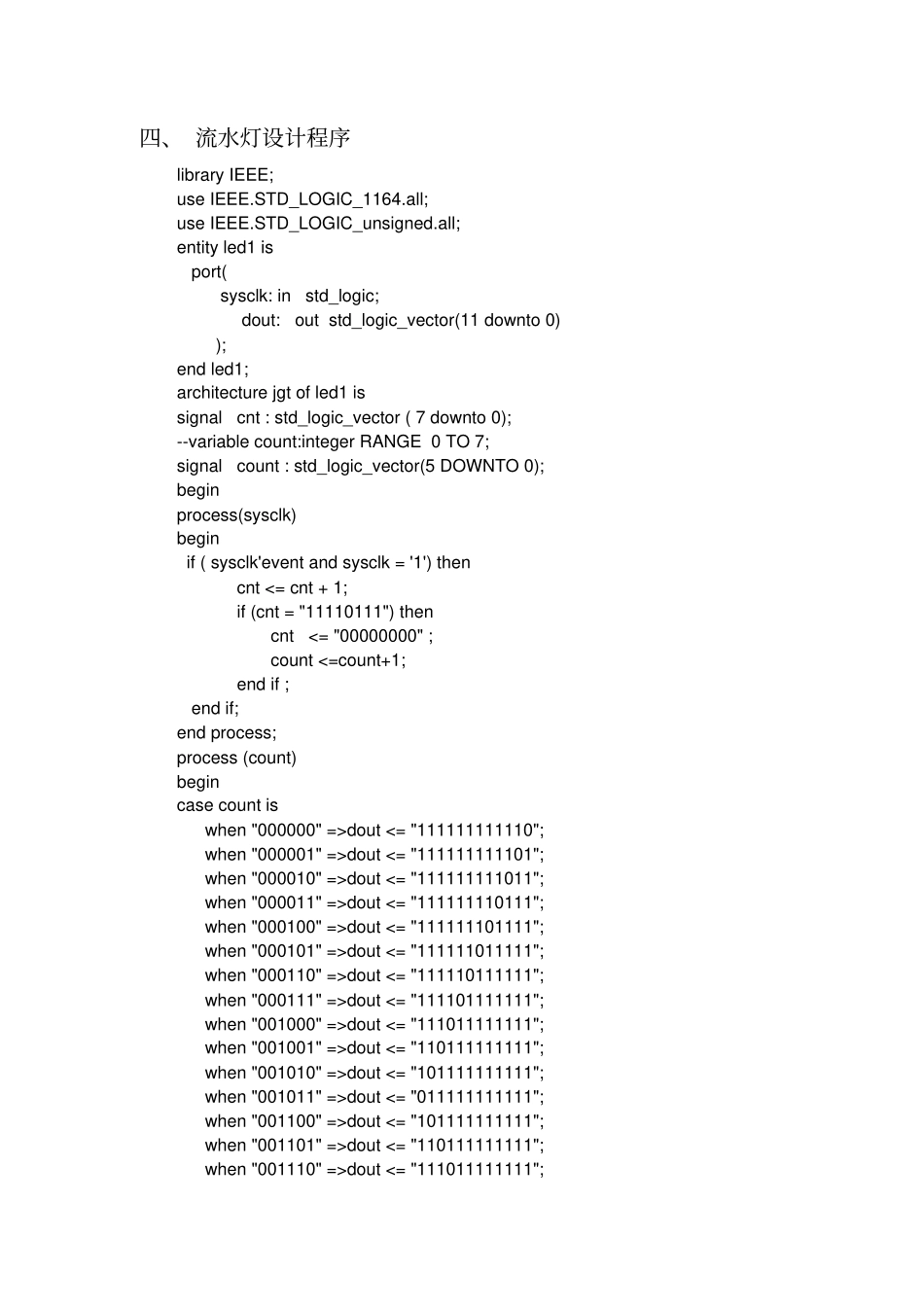

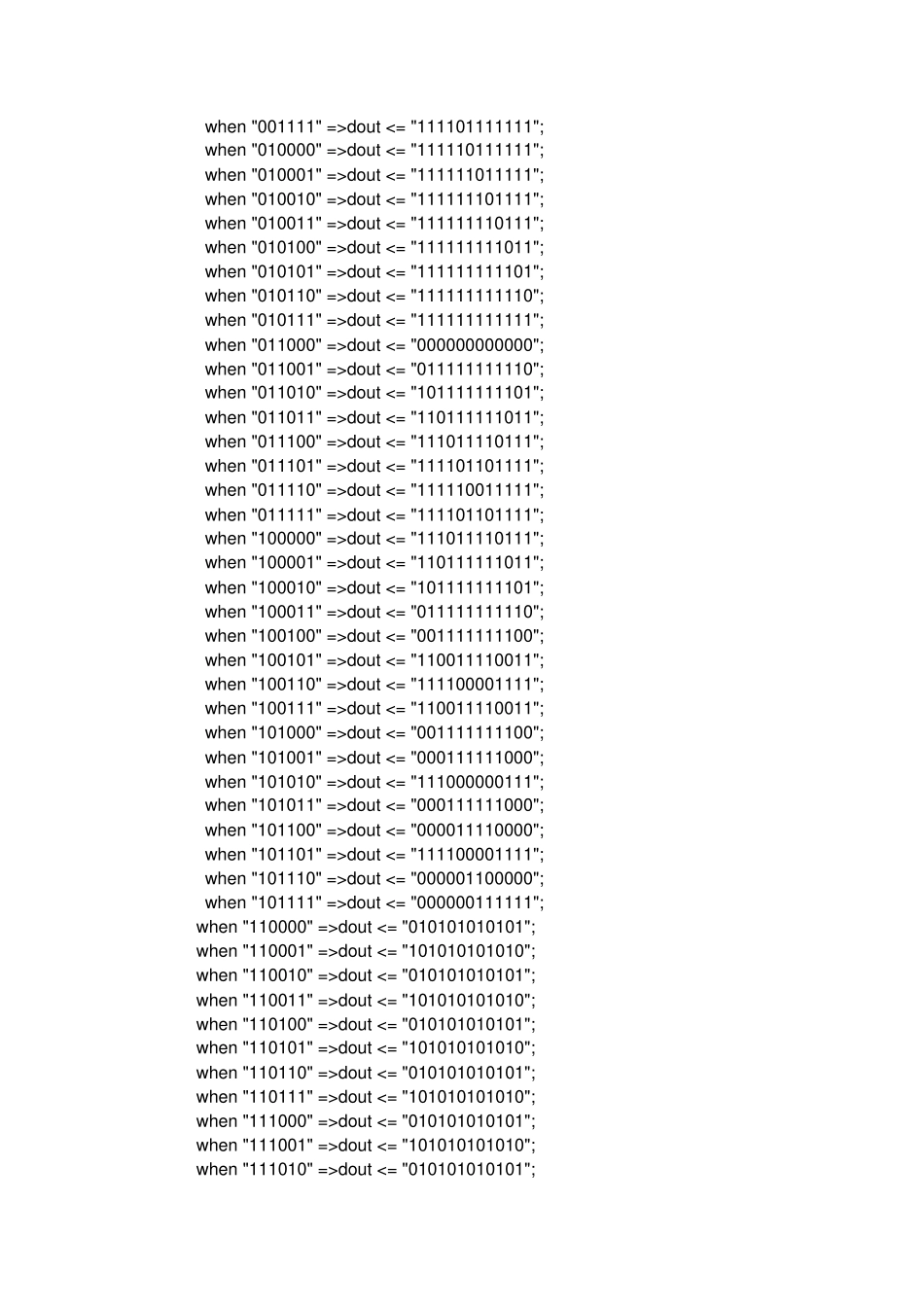

基于 VHDL流水灯的设计电子信息科学与技术刘敏 何磊 成江波一、 设计内容流水灯是一串按一定的规律像流水一样连续闪亮,流水灯控制是可编程控制器的一个应用, 其控制思想在工业控制技术领域也同样适用。流水灯控制可用多种方法实现, 但对现代可编程控制器而言, 基于 EDA技术的流水灯设计也是很普遍的。要求采用可编程逻辑器件实现一个流水灯控制电路,12 个 LED灯能连续发出 4 种不同的流水显示形式。 彩灯控制器的第 1 种花样为彩灯按顺时针方向逐次点亮; 第 2 种花样为彩灯按逆时针方向逐次点亮,然后全灭全亮; 第 3 种花样为彩灯两边同时亮1、2、3、4、5、6 个逐次向中间移动再散开;第4 种花样为彩灯连续交叉闪烁。多个花样自动变换,循环往复。二、 设计方案彩灯是由 FPGA板上的 LED灯代替,有以下 4 种闪烁效果1. 彩灯按顺时针方向逐次点亮。2. 彩灯按逆时针方向逐次点亮,然后全灭全亮。3. 彩灯两边同时亮 1、2、3、4、5、6 个逐次向中间移动再散开。4. 彩灯连续交叉闪烁。本控制电路采用 VHDL语言设计。运用自顶而下的设计思想,按功能逐层分割实现层次化设计。 根据多路彩灯控制器的设计原理,分别对应彩灯的四种变化模式、利用 VHDL语言实现该功能 . 三、 系统框图脉冲信号顺序脉冲译码逻辑电路流水灯闪烁四、 流水灯设计程序library IEEE; use IEEE.STD_LOGIC_1164.all; use IEEE.STD_LOGIC_unsigned.all; entity led1 is port( sysclk: in std_logic; dout: out std_logic_vector(11 downto 0) ); end led1; architecture jgt of led1 is signal cnt : std_logic_vector ( 7 downto 0); --variable count:integer RANGE 0 TO 7; signal count : std_logic_vector(5 DOWNTO 0); begin process(sysclk) begin if ( sysclk'event and sysclk = '1') then cnt <= cnt + 1; if (cnt = "11110111") then cnt <= "00000000" ; count <=count+1; end if ; end if; end process; process (count) begin case count is when "000000" =>dout <= "111111111110"; when "000001" =>dout <= "111111111101"; when "000010" =>dout <= "111111111011"; when "000011" =>dout <= "111111110111"; when "000100" =>dout <= "111111101111"; when "000101" =>dout <= "11111101111...