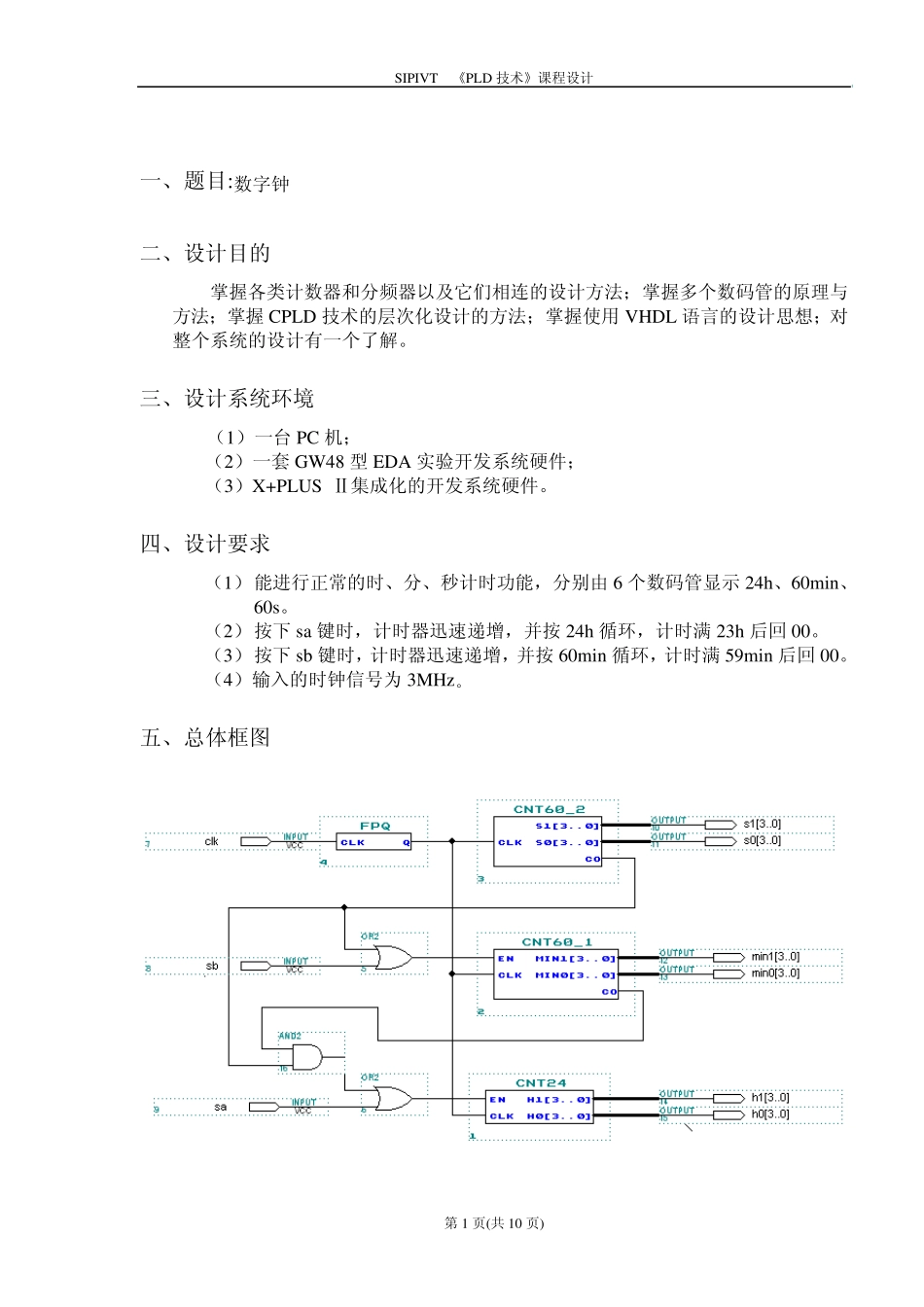

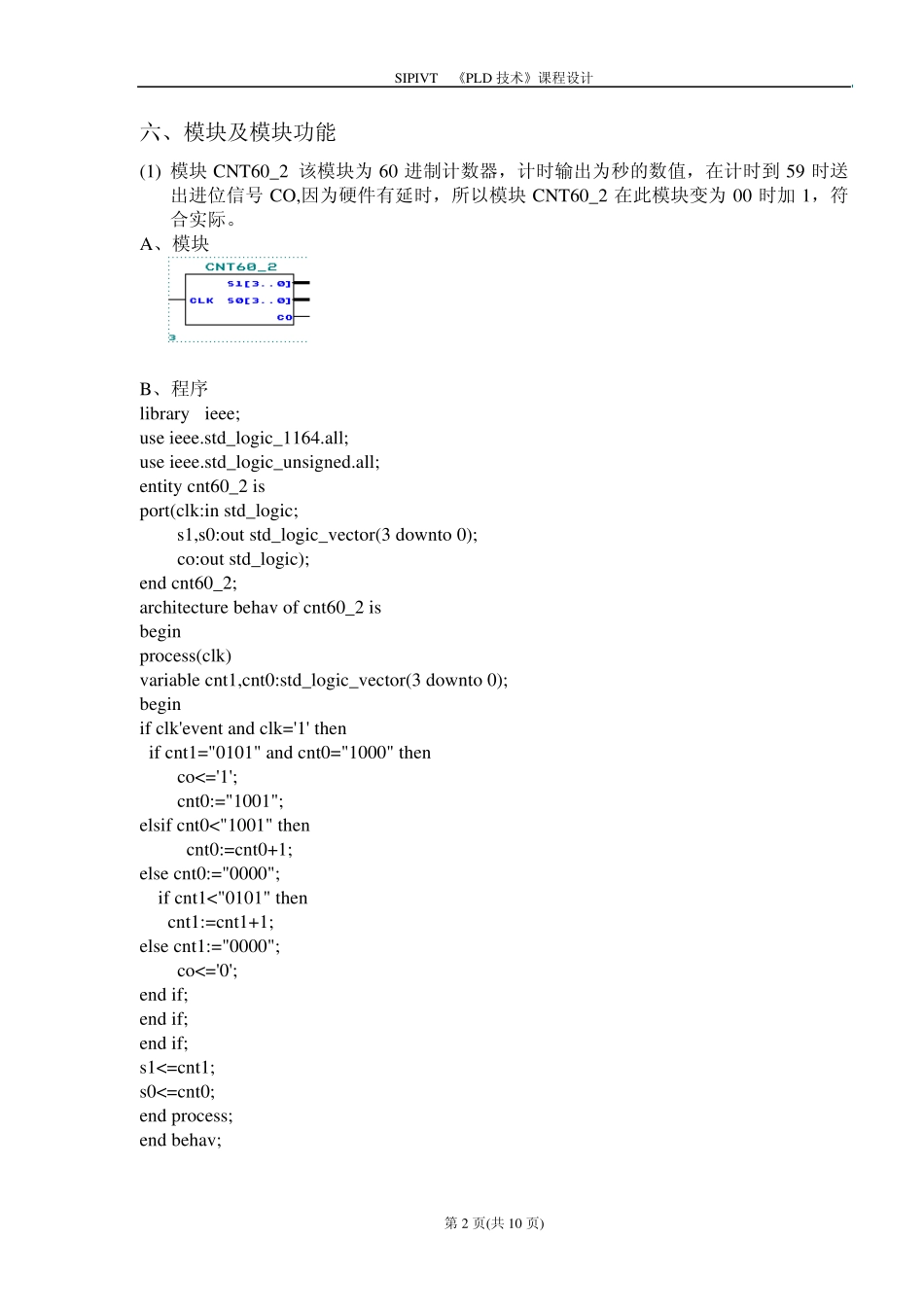

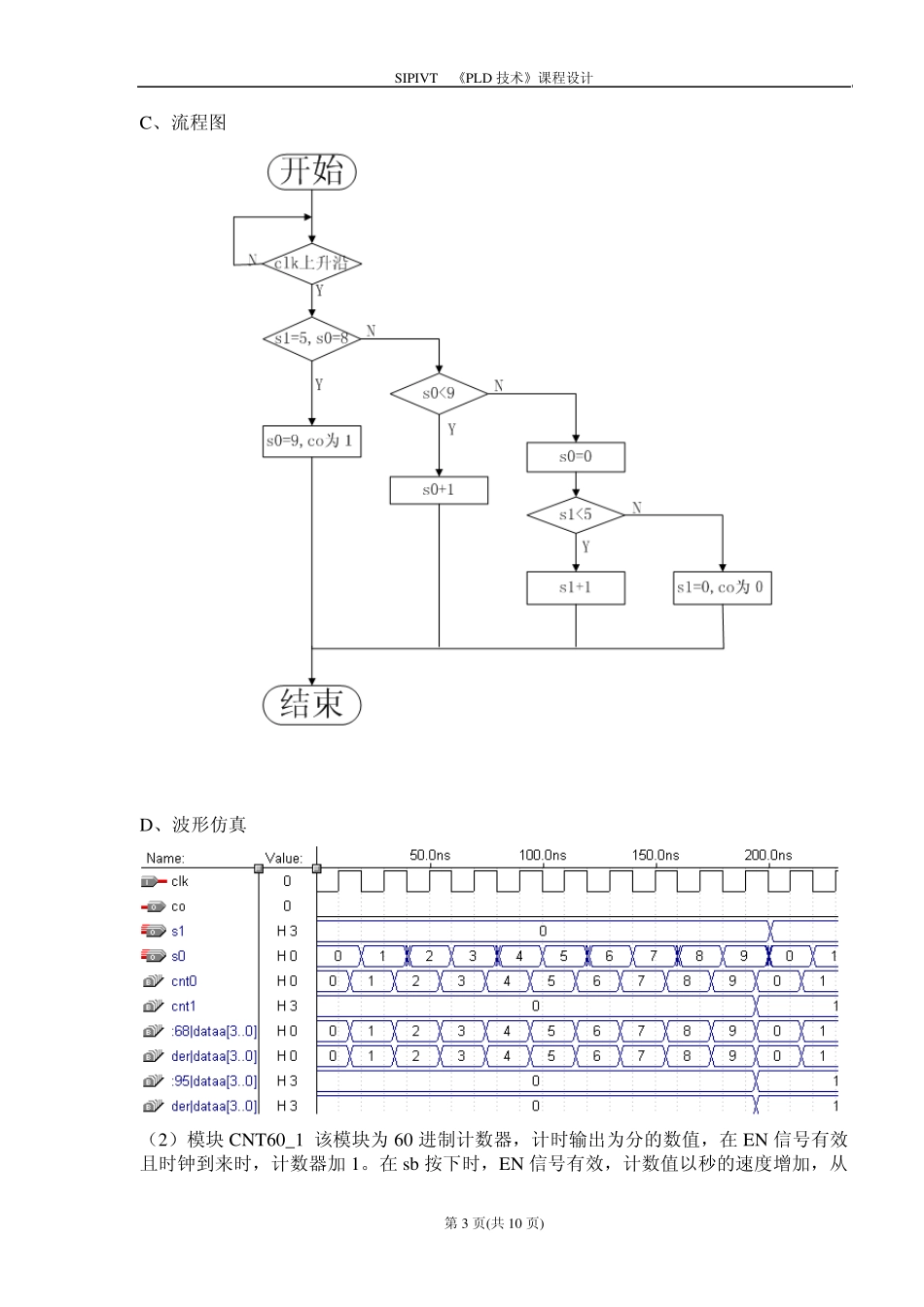

SIPIVT 《PLD 技术》课程设计 第1 页(共10 页) 一、题目:数字钟 二、设计目的 掌握各类计数器和分频器以及它们相连的设计方法;掌握多个数码管的原理与方法;掌握CPLD 技术的层次化设计的方法;掌握使用VHDL 语言的设计思想;对整个系统的设计有一个了解。 三、设计系统环境 (1)一台PC 机; (2)一套GW48 型EDA 实验开发系统硬件; (3)X+PLUS Ⅱ集成化的开发系统硬件。 四、设计要求 (1) 能进行正常的时、分、秒计时功能,分别由 6 个数码管显示 24h、60min、60s。 (2) 按下 sa 键时,计时器迅速递增,并按 24h 循环,计时满 23h 后回 00。 (3) 按下 sb 键时,计时器迅速递增,并按 60min 循环,计时满 59min 后回 00。 (4)输入的时钟信号为 3MHz。 五、总体框图 SIPIVT 《PLD 技术》课程设计 第2 页(共10 页) 六、模块及模块功能 (1) 模块 CNT60_2 该模块为 60 进制计数器,计时输出为秒的数值,在计时到 59 时送出进位信号 CO,因为硬件有延时,所以模块 CNT60_2 在此模块变为 00 时加 1,符合实际。 A、模块 B、程序 library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity cnt60_2 is port(clk:in std_logic; s1,s0:out std_logic_vector(3 downto 0); co:out std_logic); end cnt60_2; architecture behav of cnt60_2 is begin process(clk) variable cnt1,cnt0:std_logic_vector(3 downto 0); begin if clk'event and clk='1' then if cnt1="0101" and cnt0="1000" then co<='1'; cnt0:="1001"; elsif cnt0<"1001" then cnt0:=cnt0+1; else cnt0:="0000"; if cnt1<"0101" then cnt1:=cnt1+1; else cnt1:="0000"; co<='0'; end if; end if; end if; s1<=cnt1; s0<=cnt0; end process; end behav; SIPIVT 《PLD 技术》课程设计 第3 页(共10 页) C、流程图 D、波形仿真 (2)模块 CNT60_1 该模块为 60 进制计数器,计时输出为分的数值,在 EN 信号有效且时钟到来时,计数器加 1。在 sb 按下时,EN 信号有效,计数值以秒的速度增加,从SIPIVT 《PLD 技术》课程设计 第4 页(共10 页) 而实现对分钟的设置。 A、 模块 B、程序 library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity cnt...