实验一组合逻辑电路的设计1

实验目的1,掌握组合逻辑电路的功能分析与测试 2,学会设计以及实现一位全/ 减加器电路,以及舍入与检测电路设计

实验器材74LS00 二输入四与非门74LS04 六门反向器74LS10 三输入三与非门74LS86 二输入四异或门74LS73 负沿触发 JK 触发器74LS74 双 D触发器3

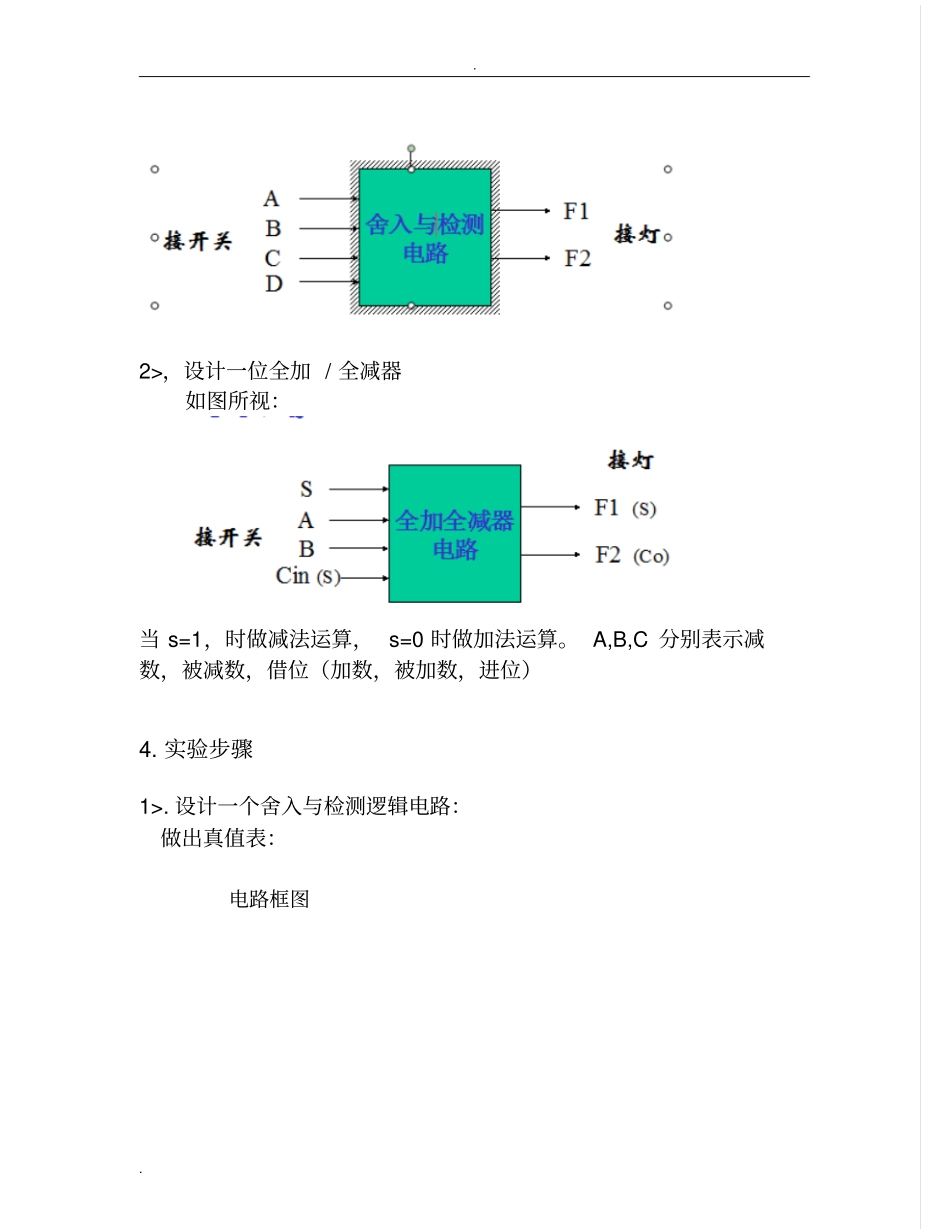

实验内容1>

设计舍入与检测的逻辑电路: 1

输入: 4 位 8421 码, 从 0000-1001 输入信号接 4 个开关,从开关输入

输出:当 8421 码>=0101(5)时,有输出F1=1 当 8421 码中 1 的个数是奇数时,有输出F2=1,

2>,设计一位全加 / 全减器如图所视:当 s=1,时做减法运算, s=0 时做加法运算

A,B,C 分别表示减数,被减数,借位(加数,被加数,进位)4

实验步骤1>

设计一个舍入与检测逻辑电路:做出真值表:电路框图

作出卡诺图,并求出F1,F2

根据 F1F2 的表达式做出电路图:按照电路图连接号电路,并且验证结果是否与设计相符

2,> 设计一位全加 / 全减器做出真值表:

F1 的卡诺图F1 卡诺图:F2 的卡诺图

按照电路图连接号电路,并且验证结果是否与设计相符

实验体会通过这次试验,我了解了用仪器拼接电路的基本情况

懂得了从电路图到真实电路的基本过程

在连接的时候,很容易因为线或者门出现问题