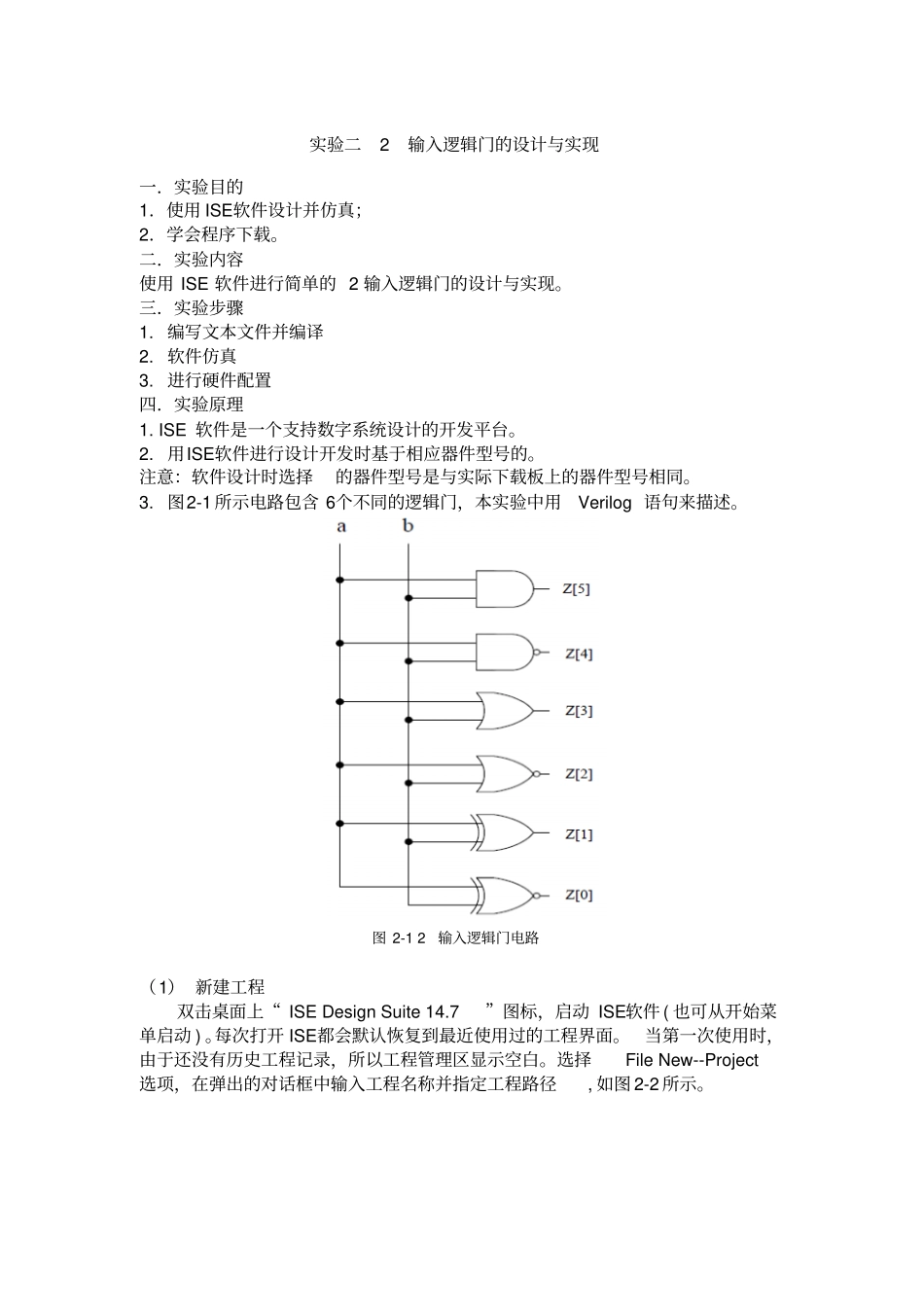

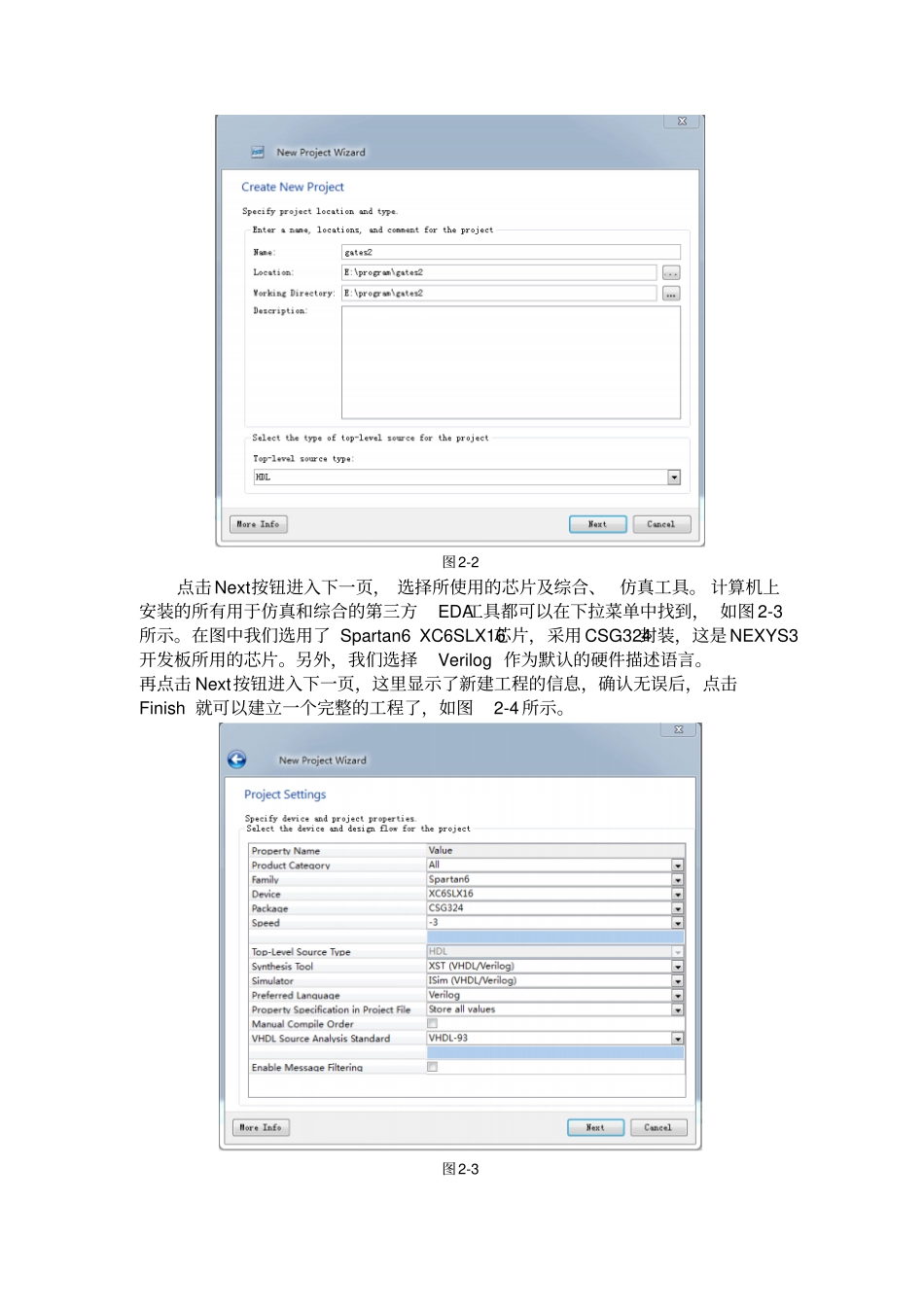

实验二 2输入逻辑门的设计与实现一.实验目的1.使用 ISE软件设计并仿真;2.学会程序下载。二.实验内容使用 ISE 软件进行简单的 2 输入逻辑门的设计与实现。三.实验步骤1. 编写文本文件并编译2. 软件仿真3. 进行硬件配置四.实验原理1. ISE 软件是一个支持数字系统设计的开发平台。2. 用ISE软件进行设计开发时基于相应器件型号的。注意:软件设计时选择的器件型号是与实际下载板上的器件型号相同。3. 图2-1 所示电路包含 6个不同的逻辑门,本实验中用Verilog 语句来描述。图 2-1 2输入逻辑门电路(1) 新建工程双击桌面上“ ISE Design Suite 14.7”图标,启动 ISE软件 ( 也可从开始菜单启动 ) 。每次打开 ISE都会默认恢复到最近使用过的工程界面。当第一次使用时,由于还没有历史工程记录,所以工程管理区显示空白。选择File New--Project选项,在弹出的对话框中输入工程名称并指定工程路径, 如图 2-2 所示。图2-2 点击 Next按钮进入下一页, 选择所使用的芯片及综合、 仿真工具。 计算机上安装的所有用于仿真和综合的第三方EDA工具都可以在下拉菜单中找到, 如图 2-3所示。在图中我们选用了 Spartan6 XC6SLX16芯片,采用 CSG324封装,这是 NEXYS3开发板所用的芯片。另外,我们选择Verilog 作为默认的硬件描述语言。再点击 Next按钮进入下一页,这里显示了新建工程的信息,确认无误后,点击Finish 就可以建立一个完整的工程了,如图2-4 所示。图2-3 图2-4 (2) 设计输入和代码仿真在工程管理区任意位置单击鼠标右键,在弹出的菜单中选择New Source命令,会弹出如图 2-5所示的新建源代码对话框,对于逻辑设计,最常用的输入方式就是 HDL代码输入法 (Verilog Module、VHDL Module)、状态机输入法 (State Diagram ) 和原理图输入法 (Schematic) 。这里我们选择 Verilog Module输入,并输入 Verilog 文件名。图2-5 单击 Next按钮进入端口定义对话框,如图2-6 所示。其中 Module Name栏用于输入模块名,这里是 gates2 ,下面的列表框用于端口的定义。Port Name表示端口名称,Direction表示端口方向 ( 可选择为 input 、output 或inout) ,MSB表示信号最高位, LSB表示信号最低位,对于单信号的MSB和LSB不用填写。当然,端口定义这一步我们也可以略过,在源程序中再行添加。图2-6 定义了模块的端口后,单击Next进入下一步,点击 Finish 完成创建。这样,ISE...