DDR 与 DDR-II DDR SDRAM DDR SDRAM全称为Dou ble Data Rate SDRAM,中文名为“双倍数据流SDRAM”

DDR SDRAM在原有的SDRAM的基础上改进而来

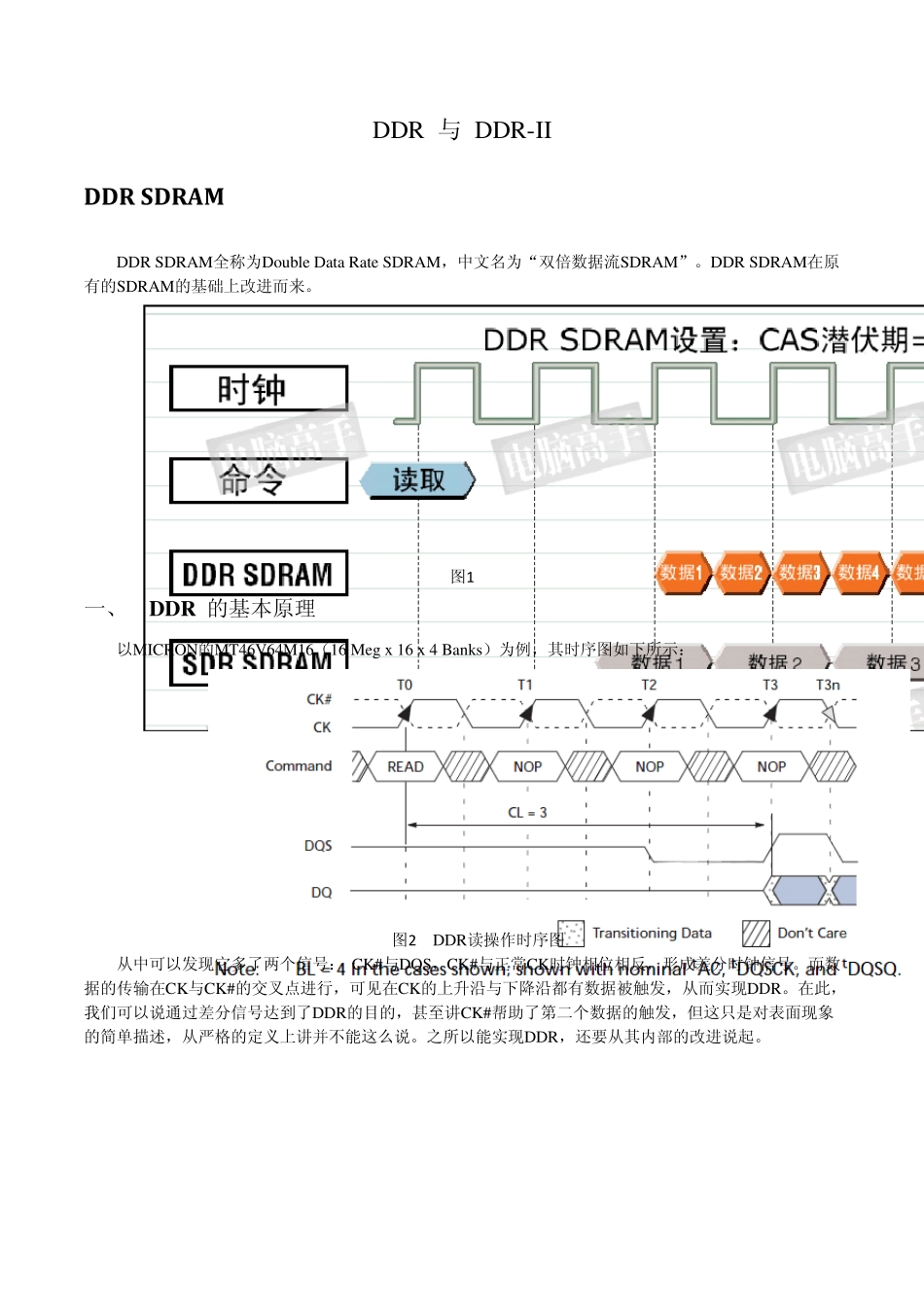

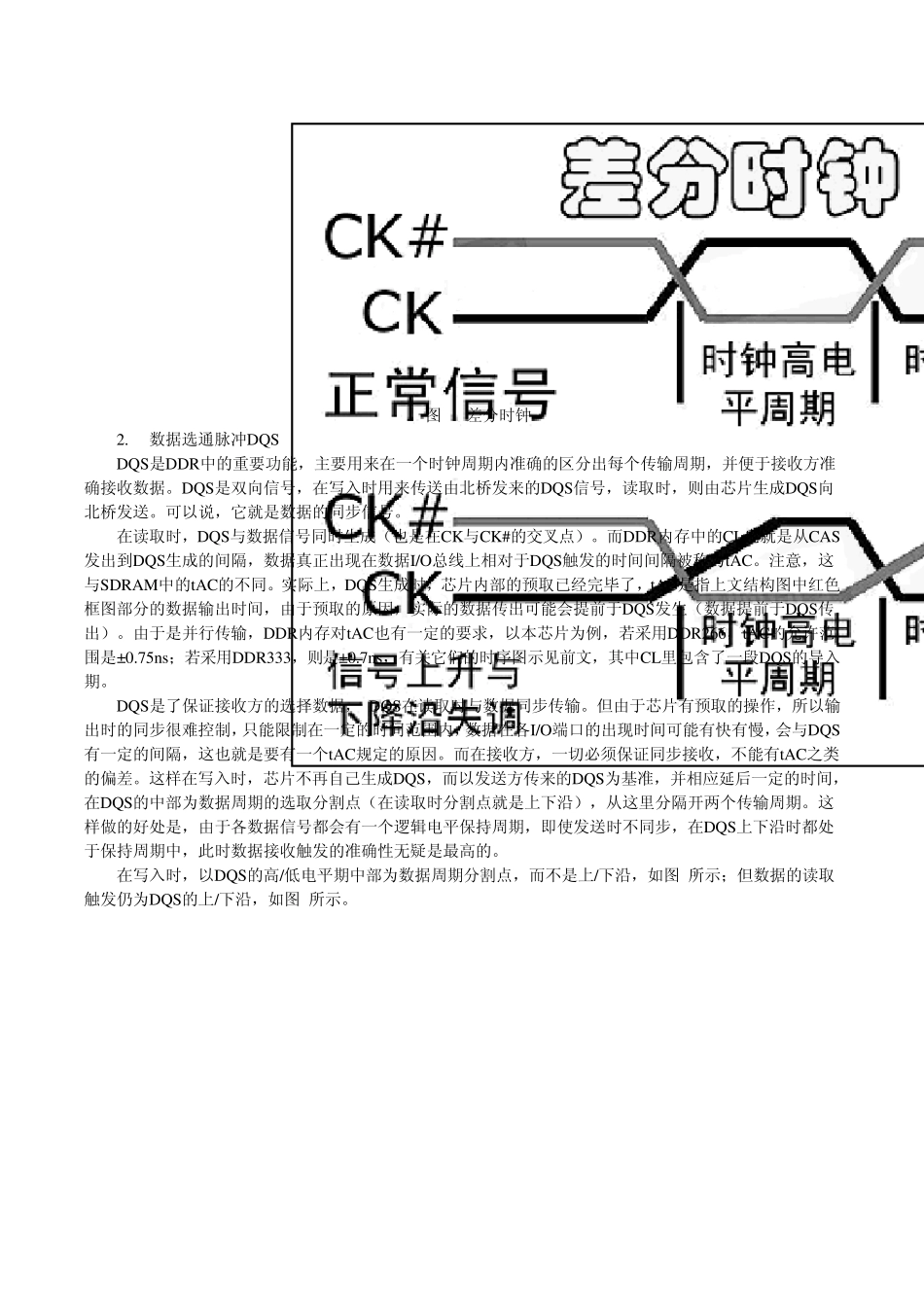

图1 一、 D D R 的基本原理 以MICRON的MT46V64M16(16 Meg x 16 x 4 Banks)为例,其时序图如下所示: 图2 DDR读操作时序图 从中可以发现它多了两个信号: CK#与DQS,CK#与正常CK时钟相位相反,形成差分时钟信号

而数据的传输在CK与CK#的交叉点进行,可见在CK的上升沿与下降沿都有数据被触发,从而实现DDR

在此,我们可以说通过差分信号达到了DDR的目的,甚至讲CK#帮助了第二个数据的触发,但这只是对表面现象的简单描述,从严格的定义上讲并不能这么说

之所以能实现DDR,还要从其内部的改进说起

图3 DDR内部结构图 从图中可以看出,其前半部分与SDRAM的结构基本相同,红色框图部分即为比SARAM多出的部分

首先不同之处就是内部的Bank control logic规格

SDRAM中Bank control logic存储单元的容量与芯片位宽相同,但在DDR中Bank control logic存储单元的容量是芯片位宽的一倍

也因此,真正的行、列地址数量也与同规格SDRAM不一样了

以本芯片为例,在读取时,Bank control logic在内部时钟信号的触发下一次传送32bit的数据给读取锁存器,再分成2路16bit 数据传给复用器,由后者将它们合并为一路16bit数据流,然后由发送器在DQS的控制下在外部时钟上升沿与下降沿分两次传输16bit的数据给北桥

这样,如果时钟频率为100MHz,那么在I/O端口处,由于是上下沿触发,那么就是传输频率就是200MHz

这种内部存储单元容量(也可以称为芯片内部总线位宽)