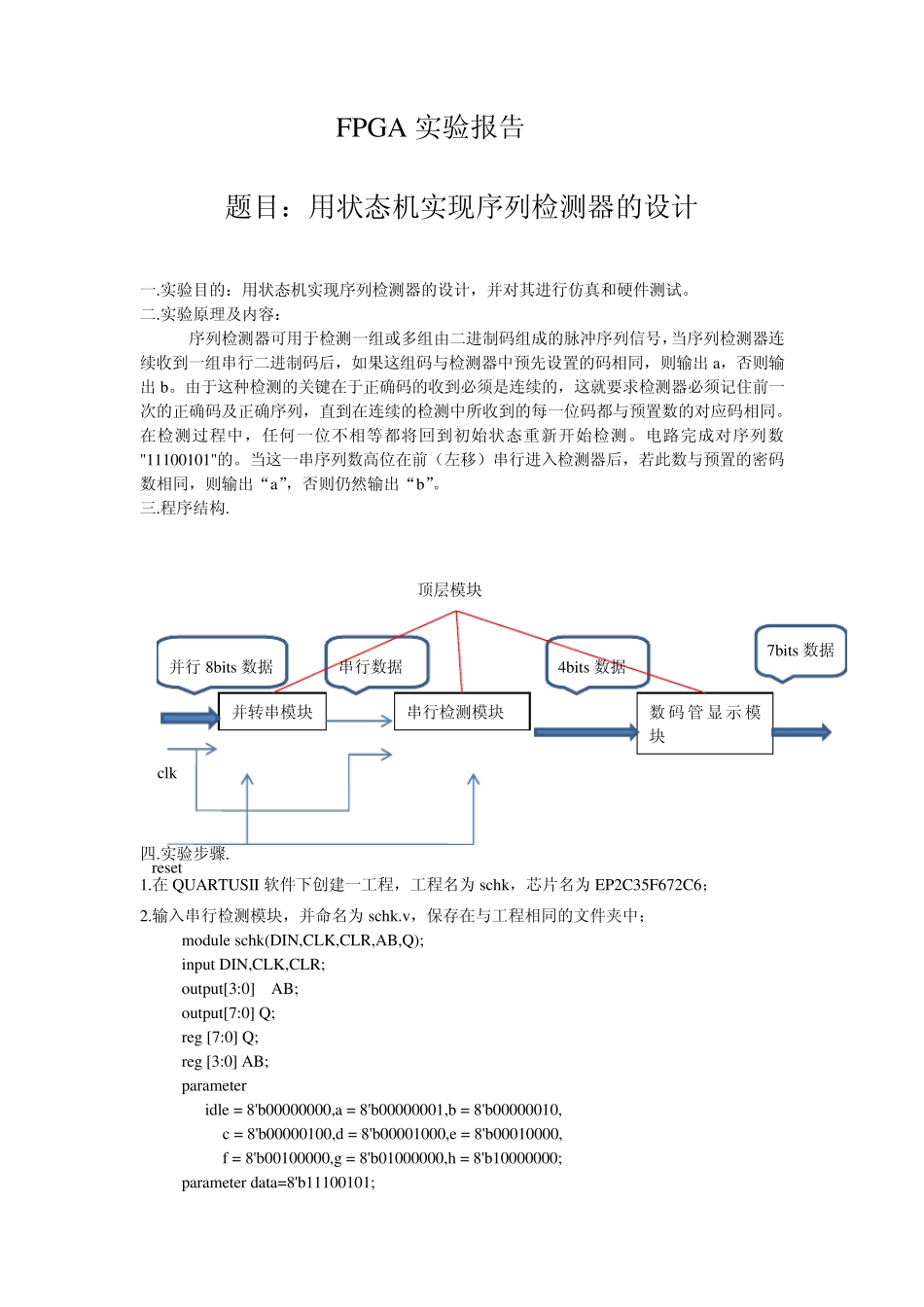

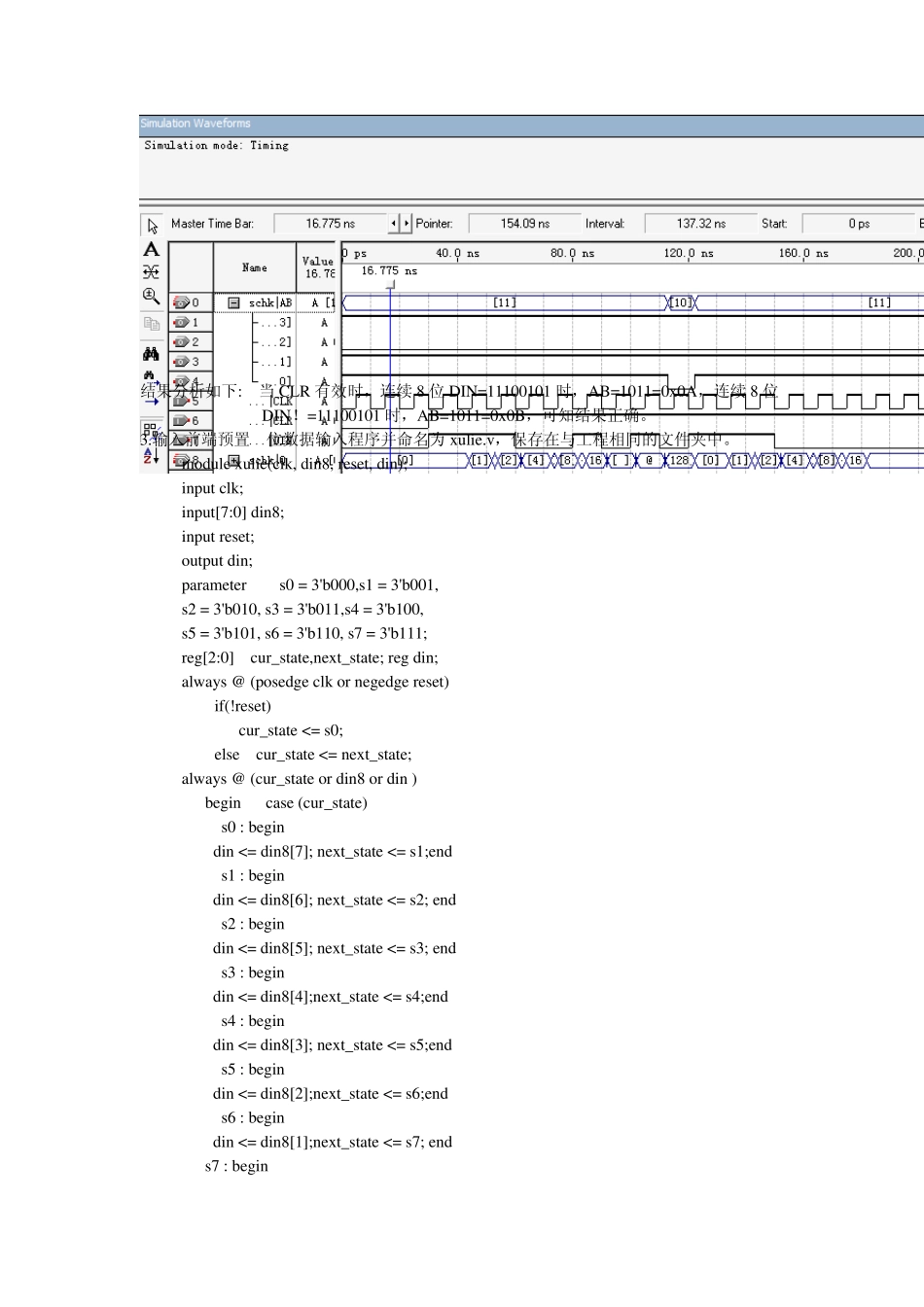

FPGA 实验报告 题目:用状态机实现序列检测器的设计 一.实验目的:用状态机实现序列检测器的设计,并对其进行仿真和硬件测试。 二.实验原理及内容: 序列检测器可用于检测一组或多组由二进制码组成的脉冲序列信号,当序列检测器连续收到一组串行二进制码后,如果这组码与检测器中预先设置的码相同,则输出a,否则输出b。由于这种检测的关键在于正确码的收到必须是连续的,这就要求检测器必须记住前一次的正确码及正确序列,直到在连续的检测中所收到的每一位码都与预置数的对应码相同。在检测过程中,任何一位不相等都将回到初始状态重新开始检测。电路完成对序列数"11100101"的。当这一串序列数高位在前(左移)串行进入检测器后,若此数与预置的密码数相同,则输出“a”,否则仍然输出“b”。 三.程序结构. 四.实验步骤. 1.在QUARTUSII 软件下创建一工程,工程名为 schk,芯片名为 EP2C35F672C6; 2.输入串行检测模块,并命名为 schk.v ,保存在与工程相同的文件夹中; modu le schk(DIN,CLK,CLR,AB,Q); inpu t DIN,CLK,CLR; ou tpu t[3:0] AB; ou tpu t[7:0] Q; reg [7:0] Q; reg [3:0] AB; parameter idle = 8'b00000000,a = 8'b00000001,b = 8'b00000010, c = 8'b00000100,d = 8'b00001000,e = 8'b00010000, f = 8'b00100000,g = 8'b01000000,h = 8'b10000000; parameter data=8'b11100101; 顶层模块 并转串模块 串行检测模块 数码管 显 示 模块 并行8bits 数据 clk 串行数据 4bits 数据 reset 7bits 数据 always @(posedge CLK or negedge CLR) if(!CLR) begin Q <= idle;end else begin case(Q) idle: begin if(DIN==data[7]) Q<=a; else Q<=idle;end a: begin if(DIN== data[6]) Q<=b; else Q<=idle;end b: begin if(DIN== data[5]) Q<=c; else Q<=idle;end c: begin if(DIN== data[4]) Q<=d; else Q<=idle;end d: begin if(DIN== data[3]) Q<=e; else Q<=idle;end e: begin if(DIN== data[2]) Q<=f; else Q<=idle;end f: begin if(DIN== data[1]) Q<=g; else Q<=idle;end g: begin if(DIN== data[0]) Q<=h; else Q<=idle;end default : Q<=idle; endcaseend always @(Q) begin if(Q==h) AB <= 4'b1010 ; else AB <= 4'b1011 ;end endmodule 其功能仿真波形和时序仿...