码和缓冲器被选通

保持时间没有表示出来,然而它是存在的

通常保持时间是通过在 WRITE 完成之后或对于 READ 是在总线上出现数据之后,延迟 SLAVE 信号一个保持时间而被加进受控设备的

而主控接收到受控信号的转变之后,使它的动作推迟一个保持时间也同样可以把保持时间加到主控设备上

全互锁异步协定的优点主要可靠性以及在处理通过较长总线连接且具有各种不同响应时间的设备时的高效率

⒊ 半同步总线 因为异步总线的传输延迟严重地限制了最高的频带宽度,因此,总线设计师结合同步和异步总线的优点设计出混合式的总线,即半同步总线,半同步总线的定时信号如图 8-4 所示

这种总线有两个控制信号,即由主控来的 CLOCK 和受控来的 WAIT 信号,它们起着异步总线 MASTER 和 SLAVE 的作用,但传输延迟是异步总线的一半,这是因为成功的握手只需要一个来回行程

对于快速设备,这种总线本质上是由时钟信号单独控制的同步总线

如果受控设备快得足以在一个时钟周期内作出响应的话,那么它就不发 WAIT 信号

这时的半同步总线像 同步总线一样地工 作

如果受控设备不能 在一个周期内作出响应,则 它就使 WAIT 信号变高,而主控设备暂停

只要 WAIT 信号高电 平 有效,其 后的时钟周期就会 知 道 主控设备处于空 闲 状态 ,当 受控设备能 响应时. 它使 WAIT 信号变低 ,而主控设备运 用标 准 同步协定的定时信号接收受控设备的回答

这样,半同步总线就具有同步总线的速度和异步总线的适 应性

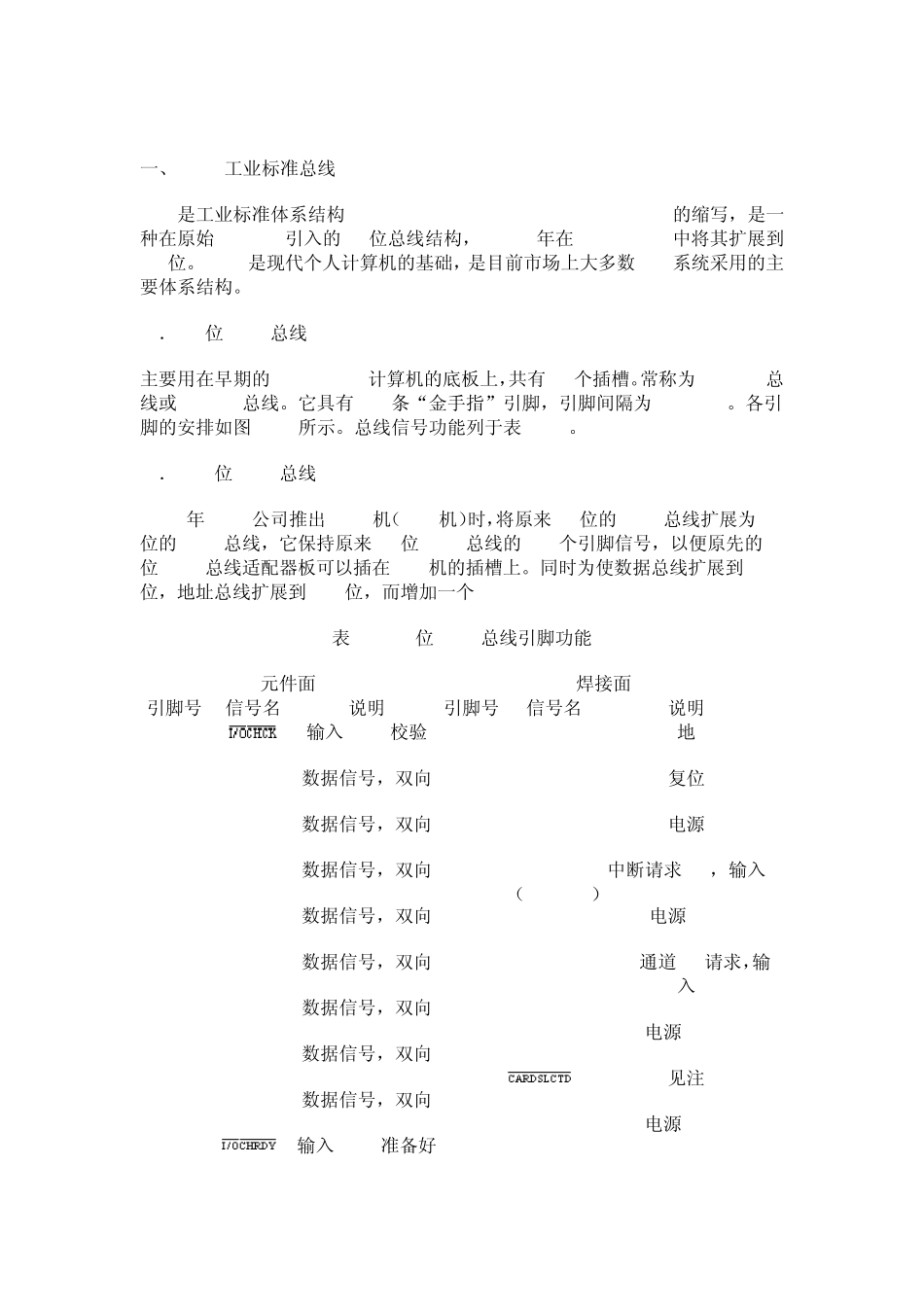

2 PC 总线 PC 总线又 称 为在板 局 部 总线

即只是单板 机 上的 I/O 扩 展 总线,不支 持多 主 CPU 的并 行处理,不存在多 CPU 共 享 资 源 ,不存在也不需要总线仲 裁

PC 机采 用开 放 式的结构 ,即在底 板 上设置 一些 标 准 扩 展