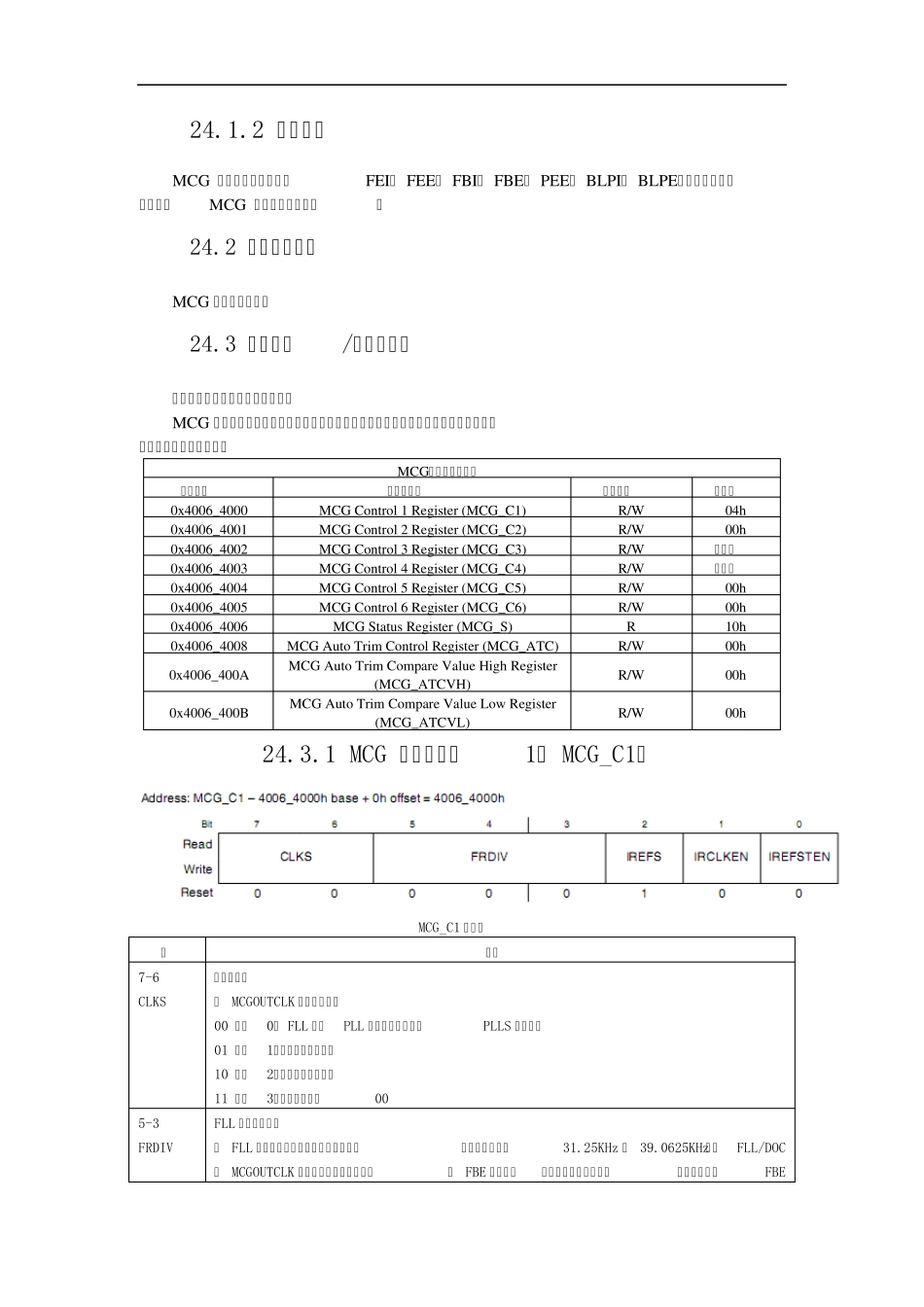

第24章 多用途时钟信号生成器(M CG) 24.1 介绍 多用途多用途时钟信号生成器(MCG)模块为MCU 提供多种时钟源选项。这个模块由一个频率环锁(FLL)和一个相位环锁(PLL)组成。FLL 可由一个内部或外部参考时钟控制,而PLL 可由一个外部参考时钟控制。这个模块要么在FLL 或 PLL 输出时钟之间,要么在内部参考时钟或外部参考时钟之间选择一个时钟源以作为MCU 系统时钟。MCG 操作与晶体振荡器有关,其中晶体振荡器允许一个外部晶体、陶瓷共振器或外部时钟源产生外部参考时钟。 24.1.1 特性 MCG 模块的关键特性: ◆频率环锁(FLL)。 ●数控石晶(DCO)。 ● DCO 可设置时钟范围有四个。 ●低频率外部参考时钟源的编程选项和最大DCO 输出频率。 ●内外参考时钟可以作为FLL 源。 ●可以作为其他片上外设的时钟源。 ◆相位环锁(PLL) ●电压控制振荡器(V CO) ●外部参考时钟作为PLL 时钟源。 ● V CO 频分模块。 ●相位/频率检测器。 ●集成环过滤器。 ●可以作为其他片上外设的时钟源。 ◆内参考时钟生成器 ● 9 个微调位的精确慢时钟 ● 4 个微调位的快时钟 ●可以被用作FLL 的时钟源。在FEI 模式下,只有慢内参考时钟(IRC)可以被用作 FLL 源。 ●无论是快时钟还是慢时钟都不能用作MCU 的时钟源 ●可以作为其他片上外设的时钟源。 ◆低功耗的石晶时钟发生器位MCG 外部参考提供控制信号: ● HGO, RANGE, EREFS ◆从晶振获得外部时钟 ●可被用作FLL 或 PLL 的时钟源 ●可被用作MCU 的时钟源 ◆从 RTC 获得外部时钟 ●只能作为 FLL 的时钟源 ●只能选择 MCU 的时钟源 ◆带有重置请求能力的外部时钟监视器,可以在 FBE,PEE,BLPE 或者 FEE 模式下对外部时钟进行监测 ◆在 PLL 中使用的有中断请求能力的锁检测器 ◆外时钟参考的内参考时钟自动裁切功能(ATM)。 ◆FLL 和 PLL 的参考分频。 ◆为其他片上设备提供时钟源的MCG PLL 时钟(MCGPLLCLK) ◆为其他片上设备提供时钟源的MCG FLL 时钟(MCGPLLCLK) ◆为其他片上设备提供时钟源的MCG Fix ed Frequ ency 时钟(MCGPLLCLK) ◆为其他片上设备提供时钟源的MCG 内参考时钟(MCGPLLCLK) 图 24-1 多用途时钟生成器(MCG)框图 24.1.2 运行模式 MCG 共有九中运行模式:FEI, FEE, FBI, FBE, PEE, BLPI, BLPE,和终止模式。详细请见MCG 模式操作(章节)。 24.2 外部引脚...