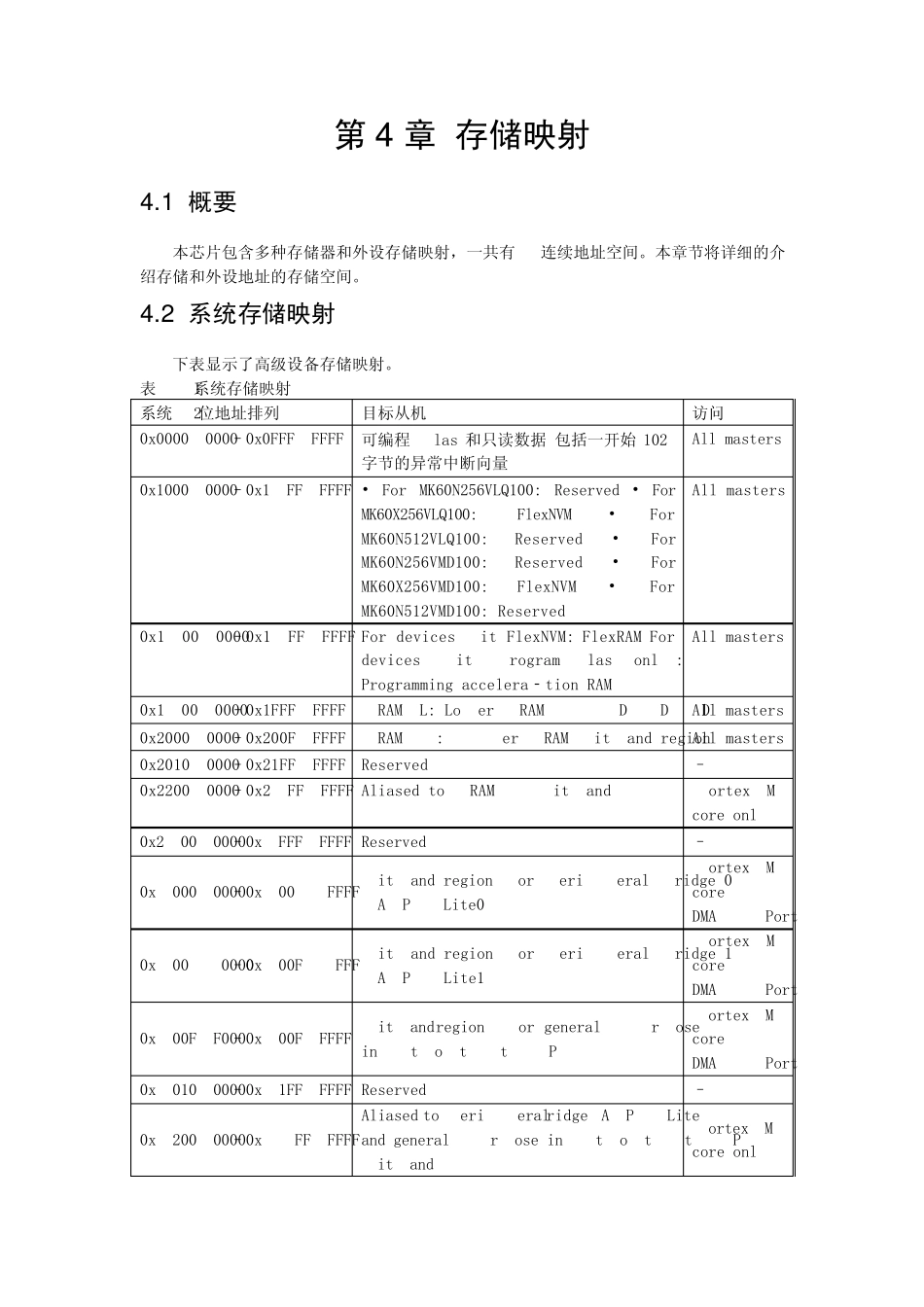

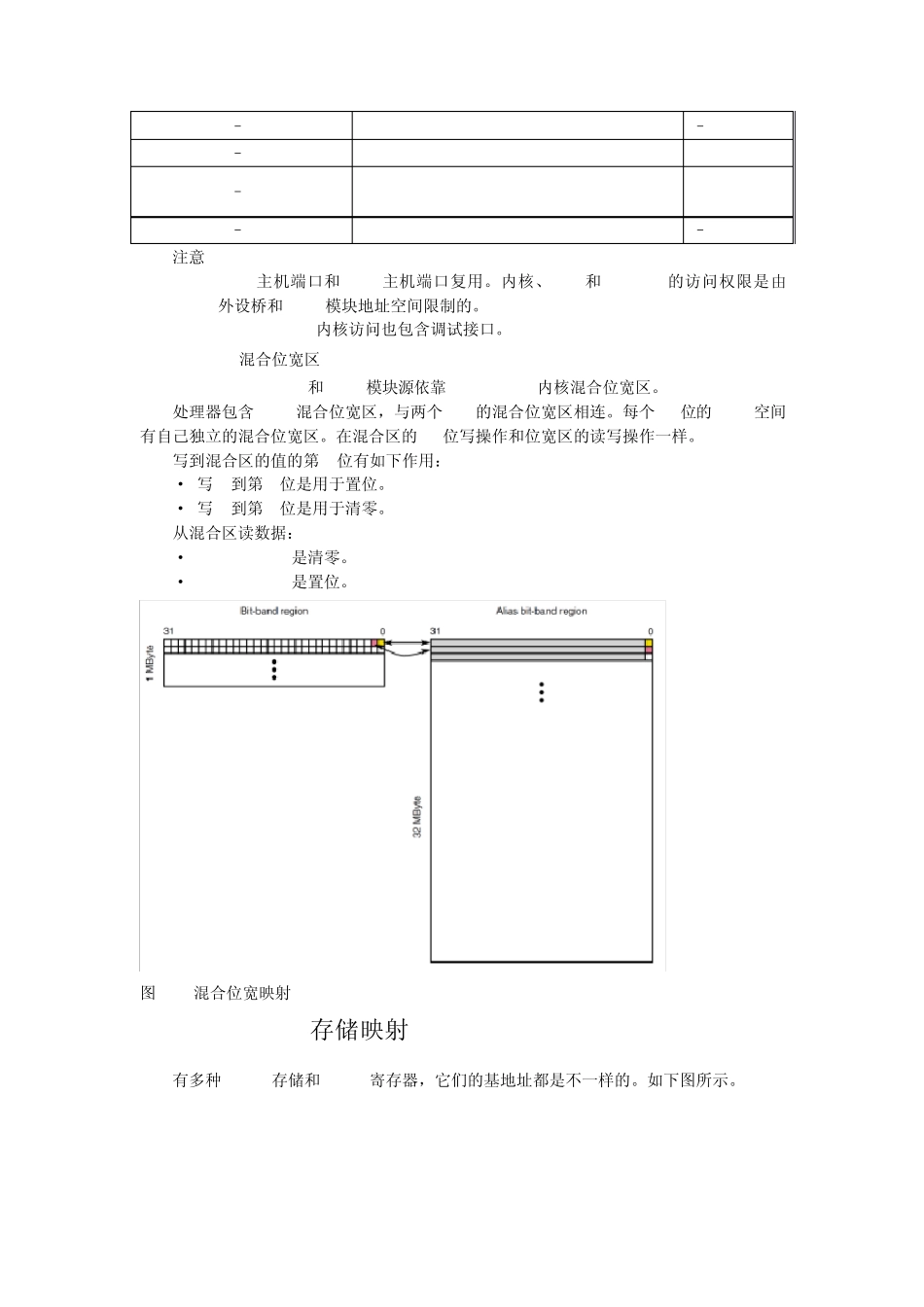

第4 章 存储映射 4 .1 概要 本芯片包含多种存储器和外设存储映射,一共有4G连续地址空间。本章节将详细的介绍存储和外设地址的存储空间。 4 .2 系统存储映射 下表显示了高级设备存储映射。 表4-1 系统存储映射 系统32位地址排列 目标从机 访问 0x0000_0000–0x0FFF_FFFF 可编程flash和只读数据(包括一开始1024字节的异常中断向量) All masters 0x1000_0000–0x13FF_FFFF • For MK60N256VLQ100: Reserved • For MK60X256VLQ100: FlexNVM • For MK60N512VLQ100: Reserved • For MK60N256VMD100: Reserved • For MK60X256VMD100: FlexNVM • For MK60N512VMD100: Reserved All masters 0x1400_0000–0x17FF_FFFF For devices with FlexNVM: FlexRAM For devices with program flash only: Programming accelera‐ tion RAM All masters 0x1800_0000–0x1FFF_FFFF SRAM_L: Lower SRAM (ICODE/DCODE) All masters 0x2000_0000–0x200F_FFFF SRAM_U: Upper SRAM bitband region All masters 0x2010_0000–0x21FF_FFFF Reserved – 0x2200_0000–0x23FF_FFFF Aliased to SRAM_U bitband Cortex-M4 core only 0x2400_0000–0x3FFF_FFFF Reserved – 0x4000_0000–0x4007_FFFF Bitband region for peripheral bridge 0 (AIPS-Lite0) Cortex-M4 core & DMA/EzPort 0x4008_0000–0x400F_EFFF Bitband region for peripheral bridge 1 (AIPS-Lite1) Cortex-M4 core & DMA/EzPort 0x400F_F000–0x400F_FFFF Bitband region for general purpose input/output (GPIO) Cortex-M4 core & DMA/EzPort 0x4010_0000–0x41FF_FFFF Reserved – 0x4200_0000–0x43FF_FFFF Aliased to peripheral bridge (AIPS-Lite) and general purpose input/output (GPIO) bitband Cortex-M4 core only 0x4400_0000–0x5FFF_FFFF Reserved – 0x6000_0000–0xDFFF_FFFF Flexbus All masters 0xE000_0000–0xE00F_FFFF Private peripherals Cortex-M4 core only 0xE010_0000–0xFFFF_FFFF Reserved – 注意 1. EzPort主机端口和DMA主机端口复用。内核、DMA和EzPort的访问权限是由AIPS-Lite外设桥和GPIO模块地址空间限制的。 2. ARM Conrtex-M4内核访问也包含调试接口。 4.2.1 混合位宽区 SRAM_U,...