可编程逻辑器件技术 项目设计报告 课题名称:七段数码管显示译码器 班 级:1 3 电子(2 )班 姓 名:许宋如 指导老师:龚兰芳 一、设计要求 1)用 VHDL 语言设计一个可以实现以下功能的程序:输入时思位二进制数,输出时对应的十进制

2)用四个开关代表四位二进制数,单个数码管显示对应的十进制数

3)编完程序之后并在开发系统上进行硬件测试

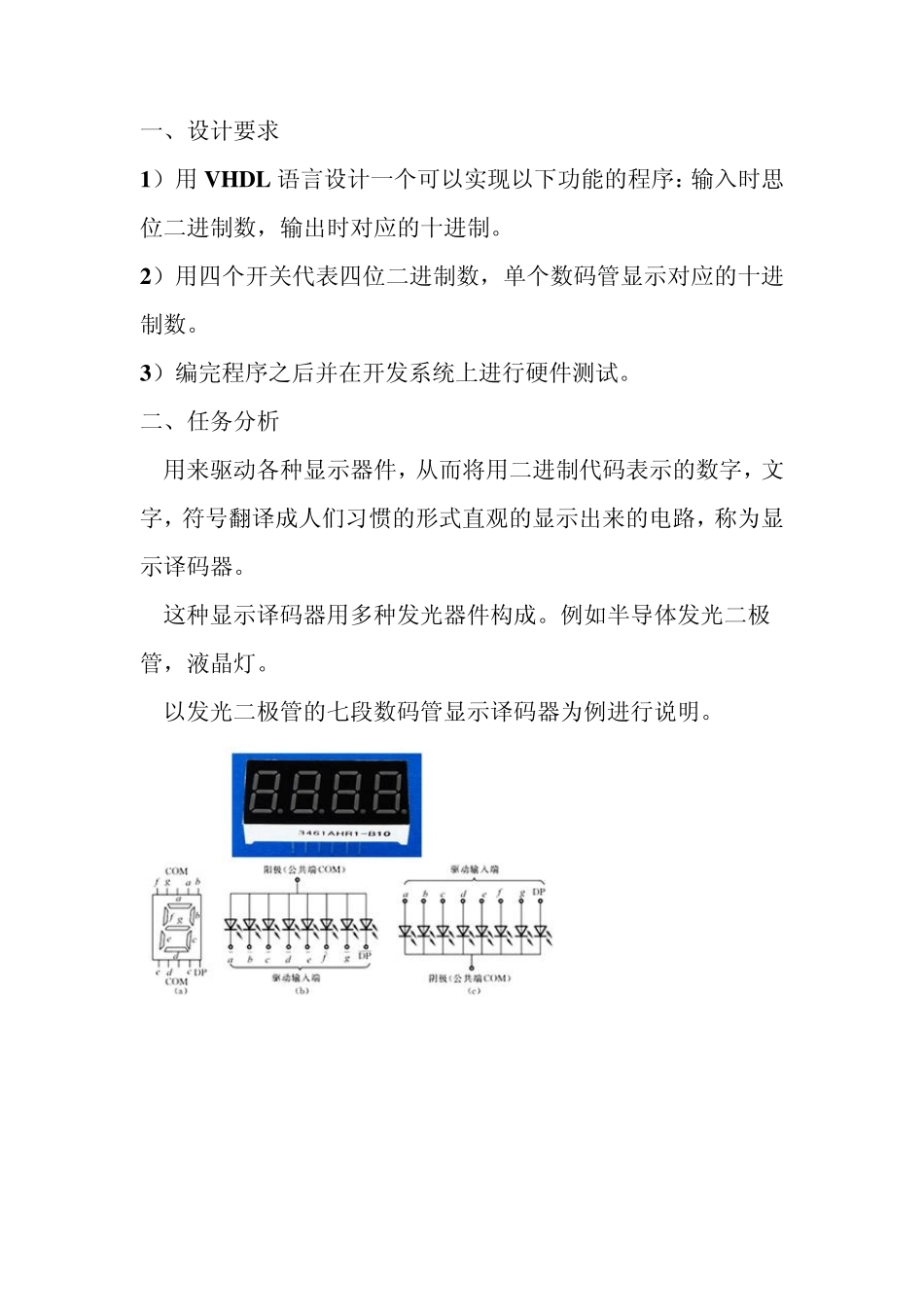

二、任务分析 用来驱动各种显示器件,从而将用二进制代码表示的数字,文字,符号翻译成人们习惯的形式直观的显示出来的电路,称为显示译码器

这种显示译码器用多种发光器件构成

例如半导体发光二极管,液晶灯

以发光二极管的七段数码管显示译码器为例进行说明

七段字形译码器的真值表: 设计原理图: 四、硬件要求 主芯片 EPM240T100C5,4个开关,一个共阴七段数码管

五、源程序 library ieee; use ieee

std_logic_1164

all; entity yima is port( l:out std_logic_vector(5 downto 0); d0,d1,d2,d3:in std_logic; a,b,c,d,e,f,g:out std_logic ); end yima; architecture behav of yima is signal m:std_logic_vector(3 downto 0); signal seg7:std_logic_vector(6 downto 0); begin l