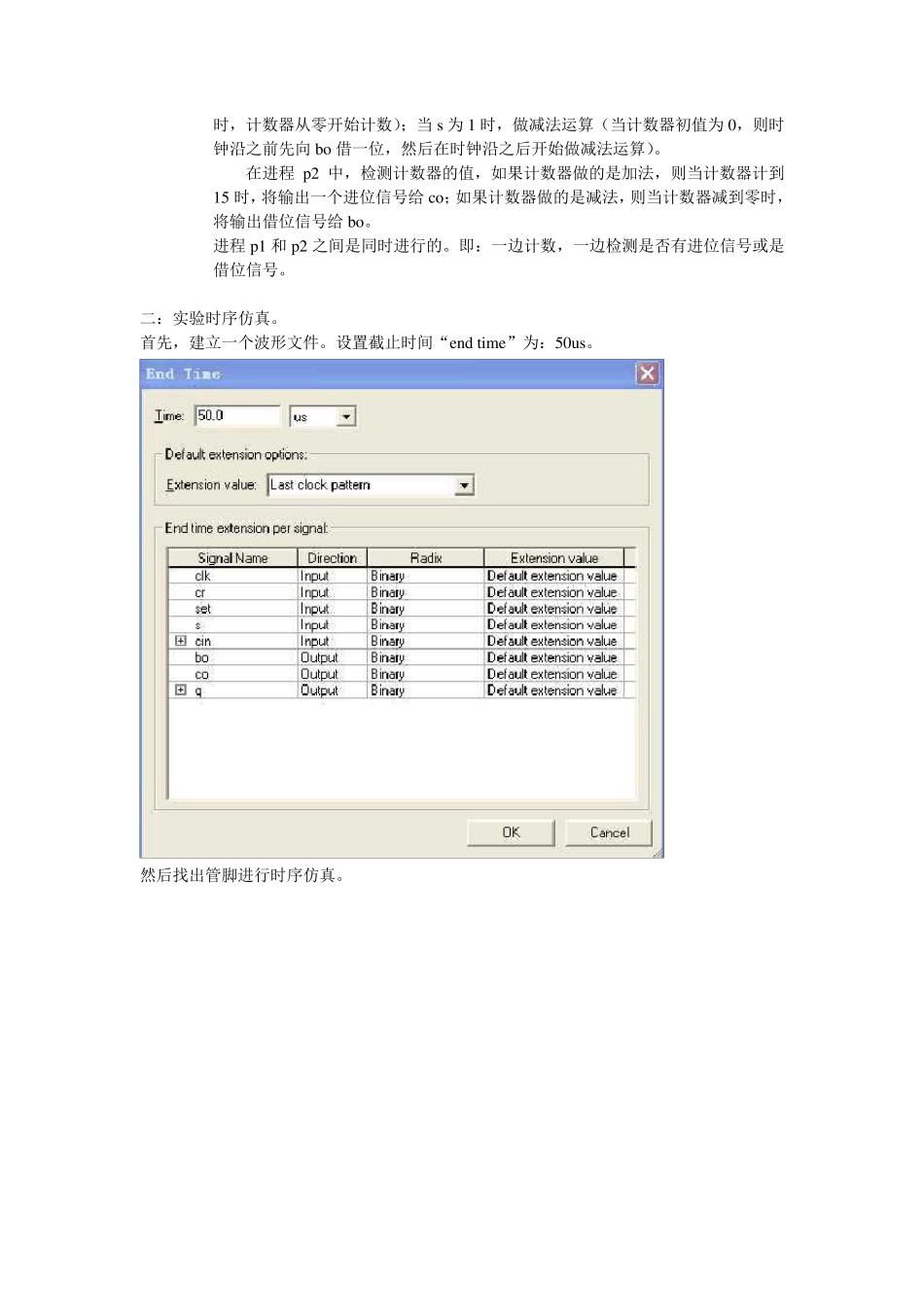

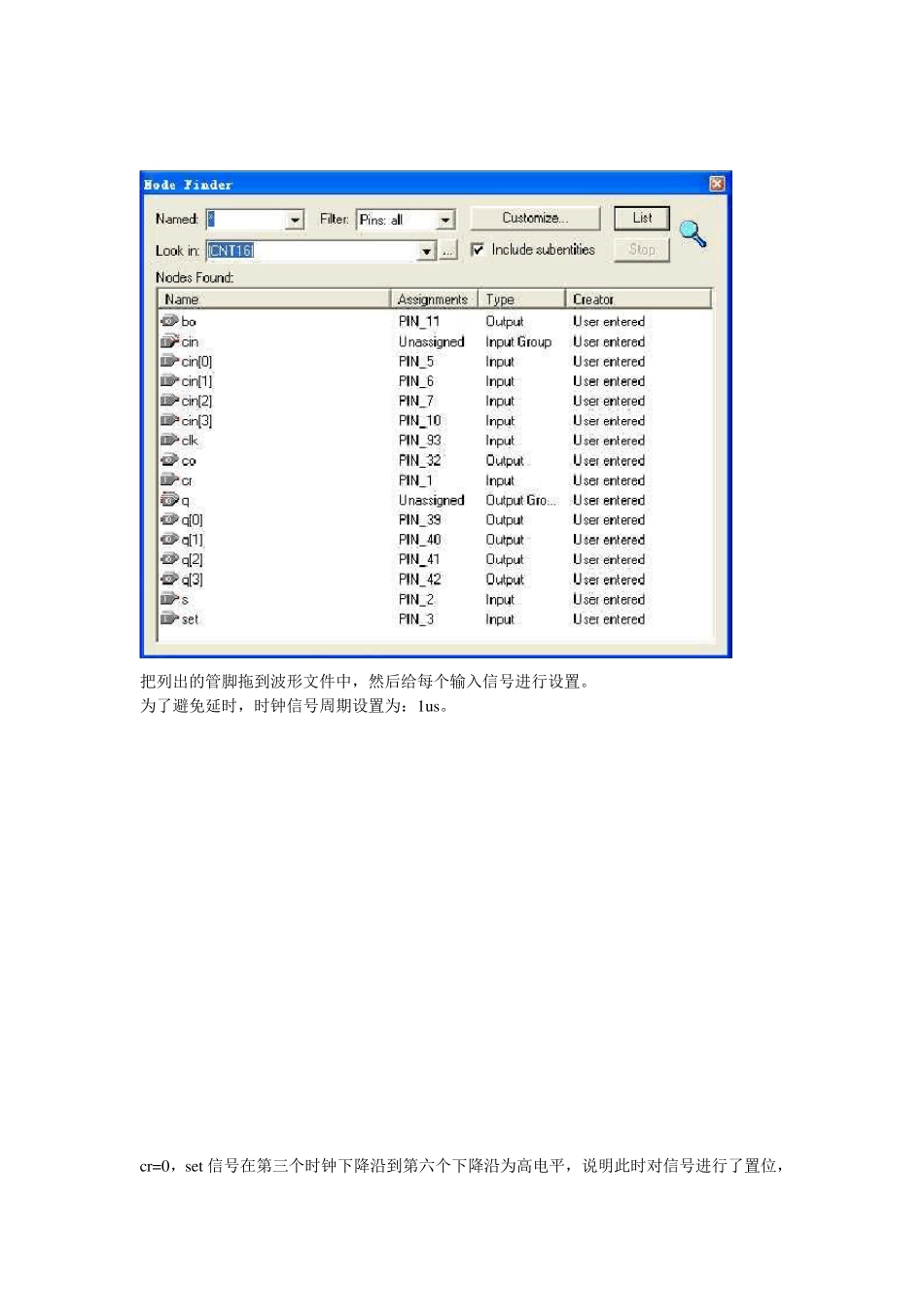

试验一:16 进制加减计数器 一: 实验程序。 实验要求:用 VHDL 语言设计一个 16 进制加减计数器,计数方向可以由外界输入信号控制,带有清零和置位,输出除了包括计数值外还应包括进位和借位。 实验程序: 程序说明:clk:为时钟信号。cr:为清零信号。set:为置位信号。s:为加减计数的方向控制信号。cin:为置位输入信号,定义为 4 位的总线形式。Co:为进位信号。 bo:为借位信号。q:为输出信号。 功能说明:在进程p1 中:当有清零信号 cr,即 cr=1 时,计数器清零。当有置位信号时,将置入的数赋给信号 po 。当有时钟的下降沿来时,并且加减方向控制信号 s 为 0 时,计数器做加法运算(如果一开机就是 4 位输出全高,则当时钟来LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY CNT16 IS PORT(clk,cr,set,s:IN std_logic; cin:IN std_logic_vector(3 DOWNTO 0); q:OUT std_logic_vector(3 DOWNTO 0); co,bo:OUT std_logic); END; ARCHITECTURE w 2 OF CNT16 IS SIGNAL po:std_logic_vector(3 DOWNTO 0); BEGIN p1:PROCESS(clk,cr,set,cin) BEGIN IF cr='1' THEN po<="0000"; elsif set='1' then po<=cin; ELSE IF clk 'EVENT AND clk='0' THEN IF s='0' THEN IF po=15 THEN po<="0000"; ELSE po<=po+1; END IF; ELSE IF po=0 THEN po<="1111"; ELSE po<=po-1; END IF; END IF; END IF; END IF; END PROCESS; p2:PROCESS(s) BEGIN IF s='0' THEN co<=po(3)AND po(2) AND po(1) AND po(0); ELSE co<='0'; bo<=NOT po(3) AND NOT po(2) AND NOT po(1) AND NOT po(0); END IF; q<=po; END PROCESS; END; 时,计数器从零开始计数);当s 为1 时,做减法运算(当计数器初值为0,则时钟沿之前先向bo 借一位,然后在时钟沿之后开始做减法运算)。 在进程p2 中,检测计数器的值,如果计数器做的是加法,则当计数器计到15 时,将输出一个进位信号给co;如果计数器做的是减法,则当计数器减到零时,将输出借位信号给bo。 进程p1 和p2 之间是同时进行的。即:一边计数,一边检测是否有进位信号或是借位信号。 二:实验时序仿真。 首先,建立一个波形文件。设置截止时间“end time”为:50u s。 然后找出管脚进行时序仿真。 把列出的管脚拖到波形文件中,然...