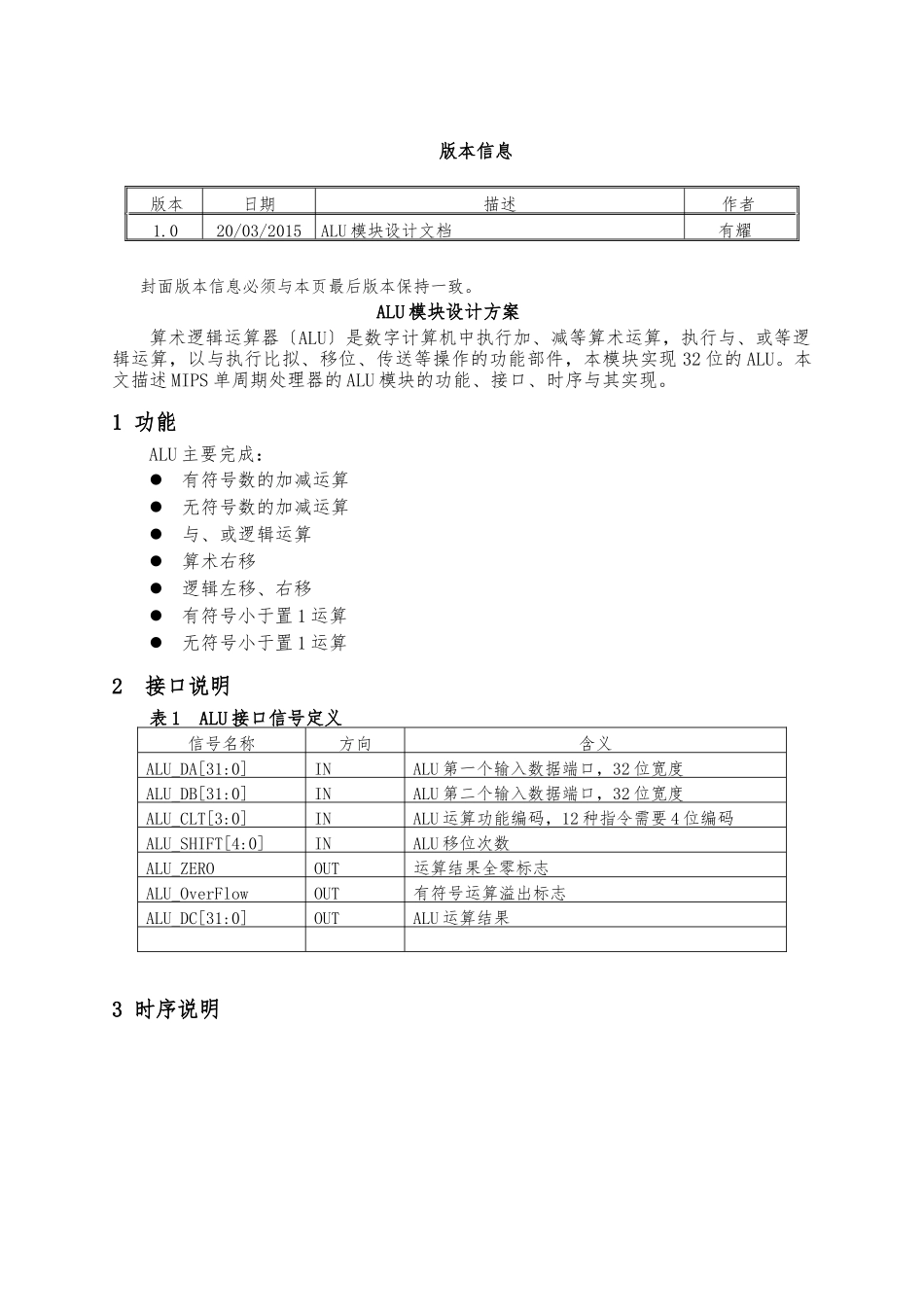

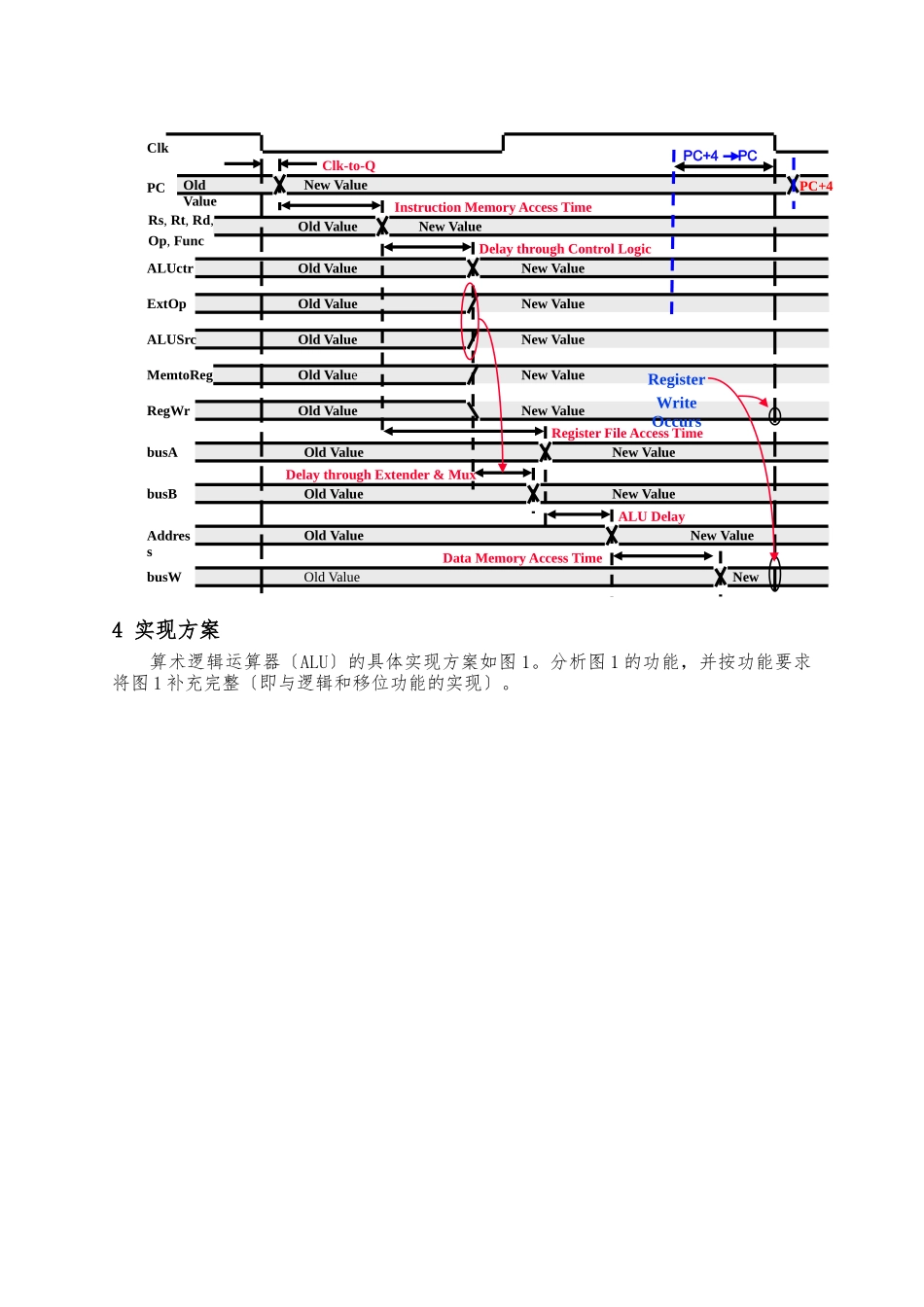

版本信息版本日期描述作者1.020/03/2015ALU 模块设计文档有耀封面版本信息必须与本页最后版本保持一致。ALU 模块设计方案算术逻辑运算器〔ALU〕是数字计算机中执行加、减等算术运算,执行与、或等逻辑运算,以与执行比拟、移位、传送等操作的功能部件,本模块实现 32 位的 ALU。本文描述 MIPS 单周期处理器的 ALU 模块的功能、接口、时序与其实现。1 功能ALU 主要完成:有符号数的加减运算无符号数的加减运算与、或逻辑运算算术右移逻辑左移、右移有符号小于置 1 运算无符号小于置 1 运算2 接口说明表 1 ALU 接口信号定义信号名称方向含义ALU_DA[31:0]INALU 第一个输入数据端口,32 位宽度ALU_DB[31:0]INALU 第二个输入数据端口,32 位宽度ALU_CLT[3:0]INALU 运算功能编码,12 种指令需要 4 位编码ALU_SHIFT[4:0]IN ALU 移位次数ALU_ZEROOUT运算结果全零标志ALU_OverFlowOUT有符号运算溢出标志ALU_DC[31:0]OUTALU 运算结果3 时序说明4 实现方案算术逻辑运算器〔ALU〕的具体实现方案如图 1。分析图 1 的功能,并按功能要求将图 1 补充完整〔即与逻辑和移位功能的实现〕。ClkPCRs, Rt, Rd,Op, FuncClk-to-QALUctrInstruction Memory Access TimeOld ValueNew ValueRegWrOld ValueNew ValueDelay through Control LogicbusARegister File Access TimeOld ValueNew ValuebusBALU DelayOld ValueNew ValueOld ValueNew ValueNew ValueOld ValueExtOpOld ValueNew ValueALUSrcOld ValueNew ValueMemtoRegOld ValueNew ValueAddressOld ValueNew ValuebusWOld ValueNewDelay through Extender & MuxRegisterWrite OccursData Memory Access TimePC+4PC+4 PC 图 1 ALU 实现方案表 1 ALU 控制信号SUBctr = ALUctr<2>〔作为加减控制信号,同时作为与或控制信号〕ANDctr = ALUctr<0>OVctr = !ALUctr<1>&ALUctr<0>SIGctr = ALUctr<0>OPctr<1> = ALUctr<2> & ALUctr<1>OPctr<0> = 〔!ALUctr<2> & ALUctr<1> & !ALUctr<0>〕| ALUctr<3>根据〔Opctr=2’b11 时作为移位输出选择〕、ALUctr<3:0>==4’b10000 逻辑左移,ALUctr<3:0>==4’b10001 逻辑右移,ALUctr<3:0>==4’b10010 算术右移等要求修改补充表 1。5 电路设计描述module (ALU_DA,ALU_DB,ALU_CLT,ALU_SHIFT,ALU_ZERO,ALU_OverFlow,ALU_DC)input [31:0] ALU_DA;input [...