通信与电子系统综合设计院系: 信息学院 6 系 姓名: 学号: 邮箱 手机: 2025 年 12 月 27 日设计一 实现 FPGA 对 CPLD 外设的全部利用实验要求•编写 CPLD 程序控制其外设(LED,数码管,输入开关等),并全部提供给 FPGA 使用•编写 CPLD 与 FPGA(XC2V2000)的接口电路,实现 FPGA 与CPLD 外设的直接对应关系

•编写 FPGA 程序测试 CPLD 的全部外设实验说明1

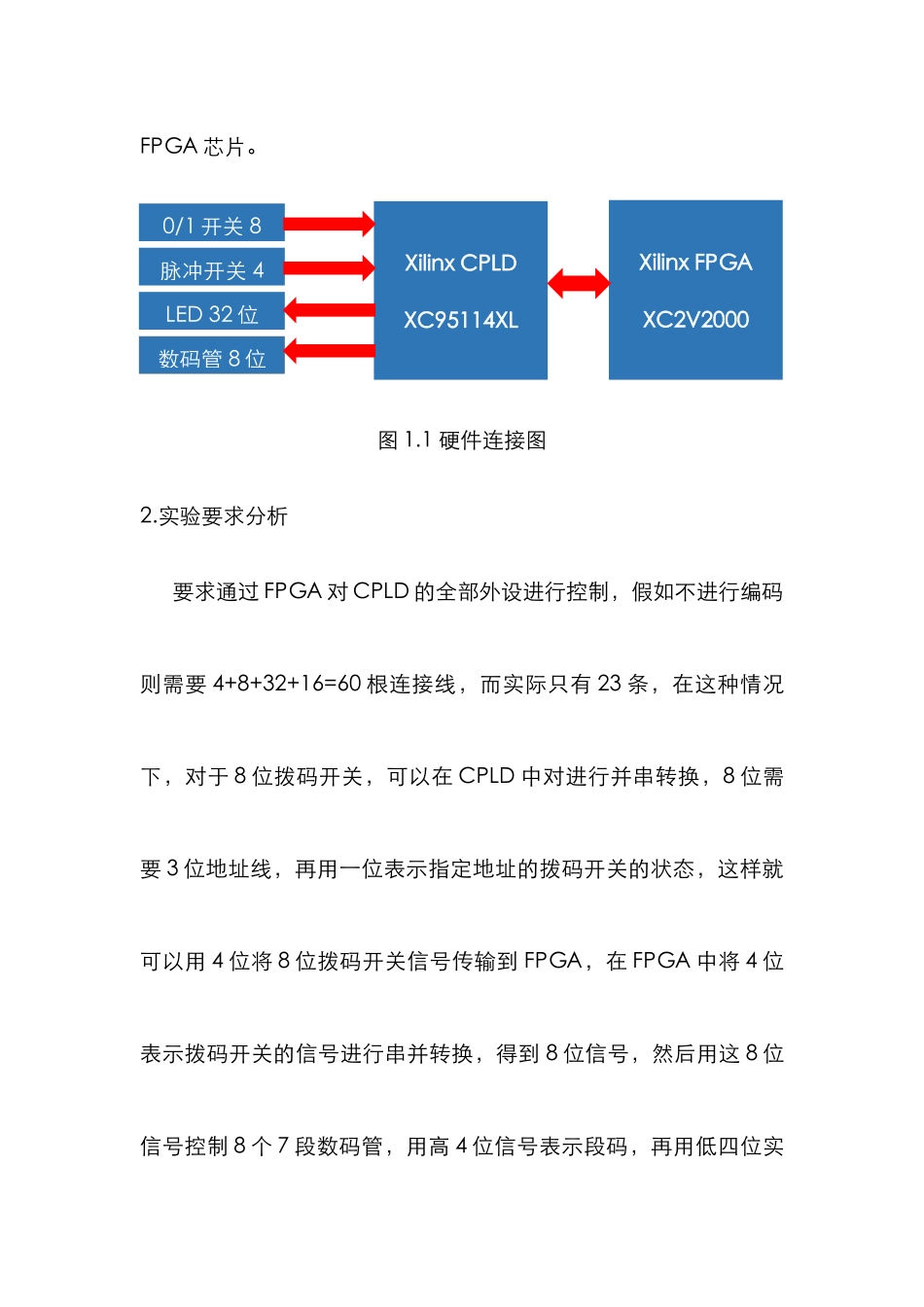

硬件分析本次实验涉及的硬件包括:4 个脉冲触发开关、8 个拨码开关、8个 7 段数码管、32 个 LED 发光二极管以及如图 1

1 所示的 CPLD 和FPGA 芯片

1 硬件连接图2

实验要求分析要求通过 FPGA 对 CPLD 的全部外设进行控制,假如不进行编码则需要 4+8+32+16=60 根连接线,而实际只有 23 条,在这种情况下,对于 8 位拨码开关,可以在 CPLD 中对进行并串转换,8 位需要 3 位地址线,再用一位表示指定地址的拨码开关的状态,这样就可以用 4 位将 8 位拨码开关信号传输到 FPGA,在 FPGA 中将 4 位表示拨码开关的信号进行串并转换,得到 8 位信号,然后用这 8 位信号控制 8 个 7 段数码管,用高 4 位信号表示段码,再用低四位实Xilinx CPLDXC95114XLXilinx FPGAXC2V20000/1 开关 8脉冲开关 4LED 32 位数码管 8 位现功能控制,最多有 16 种

对于 4 个脉冲开关,可直接传输,在FPGA 中,用这 4 位信号实现对 32 位 LED 发光二极管进行控制;此外,8 个 7 段数码管,需要 3 根地址线和 4 根数据线,32 个 LED 发光二极管,需要 5 根地址线和 1 位状态位,状态位用来表示指定地址的 LED 的状态

通过上述分析,总共