1五人多数表决器的VHDL设计1设计要求(1)五人多数表决逻辑:多数通过;(2)在主持人控制下,10秒内表决有效;(3)设主持人控制键,复位键:控制键:启动表决;复位键:系统复位

2设计说明在脉冲作用下,使用减法计数器,在初值为10秒的时候,主持人按控制键启动表决后,开始计时

每来一个脉冲计数器就减少1

一直这样下去,直到计数器变为0

计数器为0时投票无效

最后统计投票人数通过同意人数决定表决结果,当投票人不小于3人时,投票通过

在主持人按下复位键时,计数回到10,重新进行减法计数器

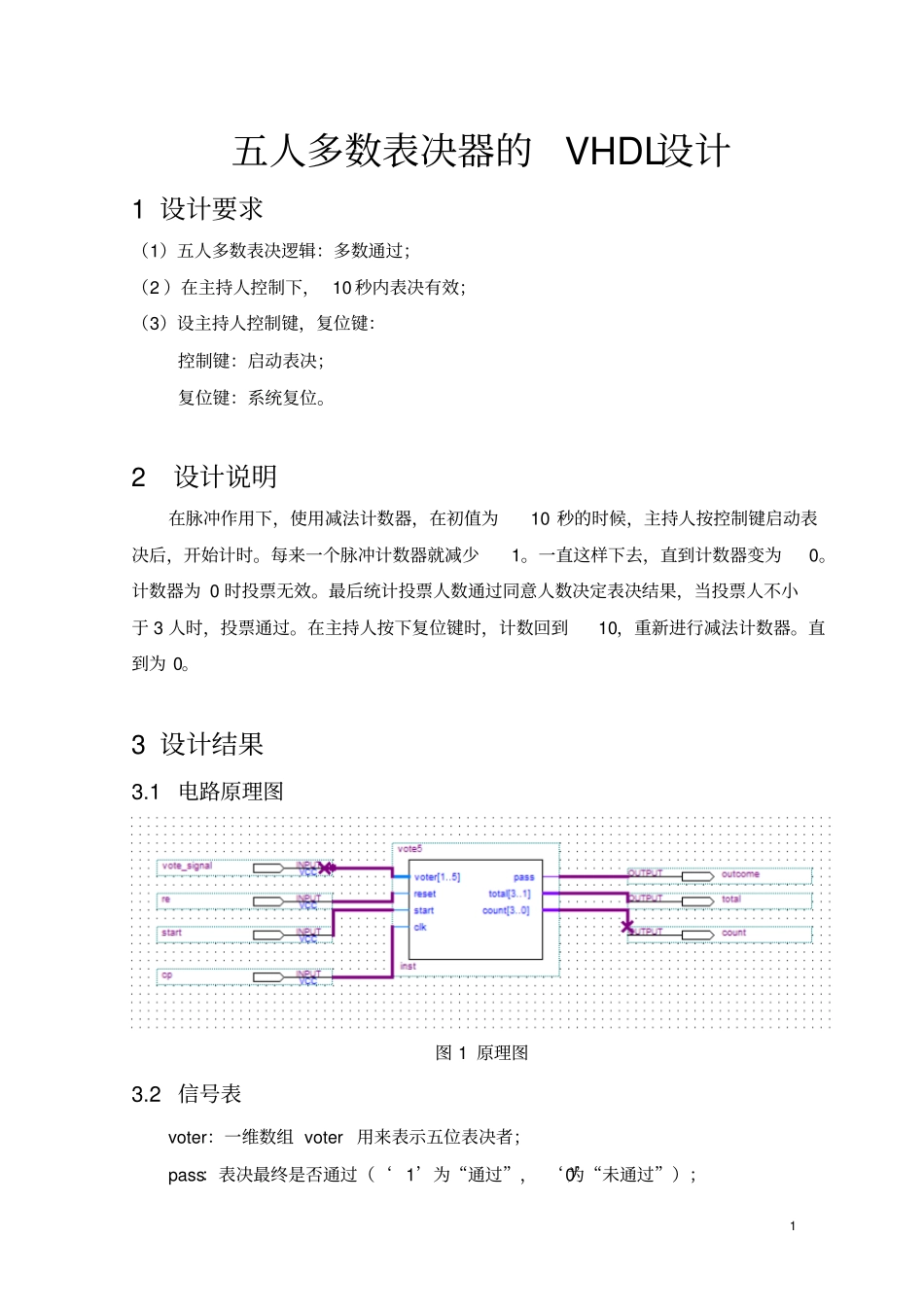

3设计结果3

1电路原理图图1原理图3

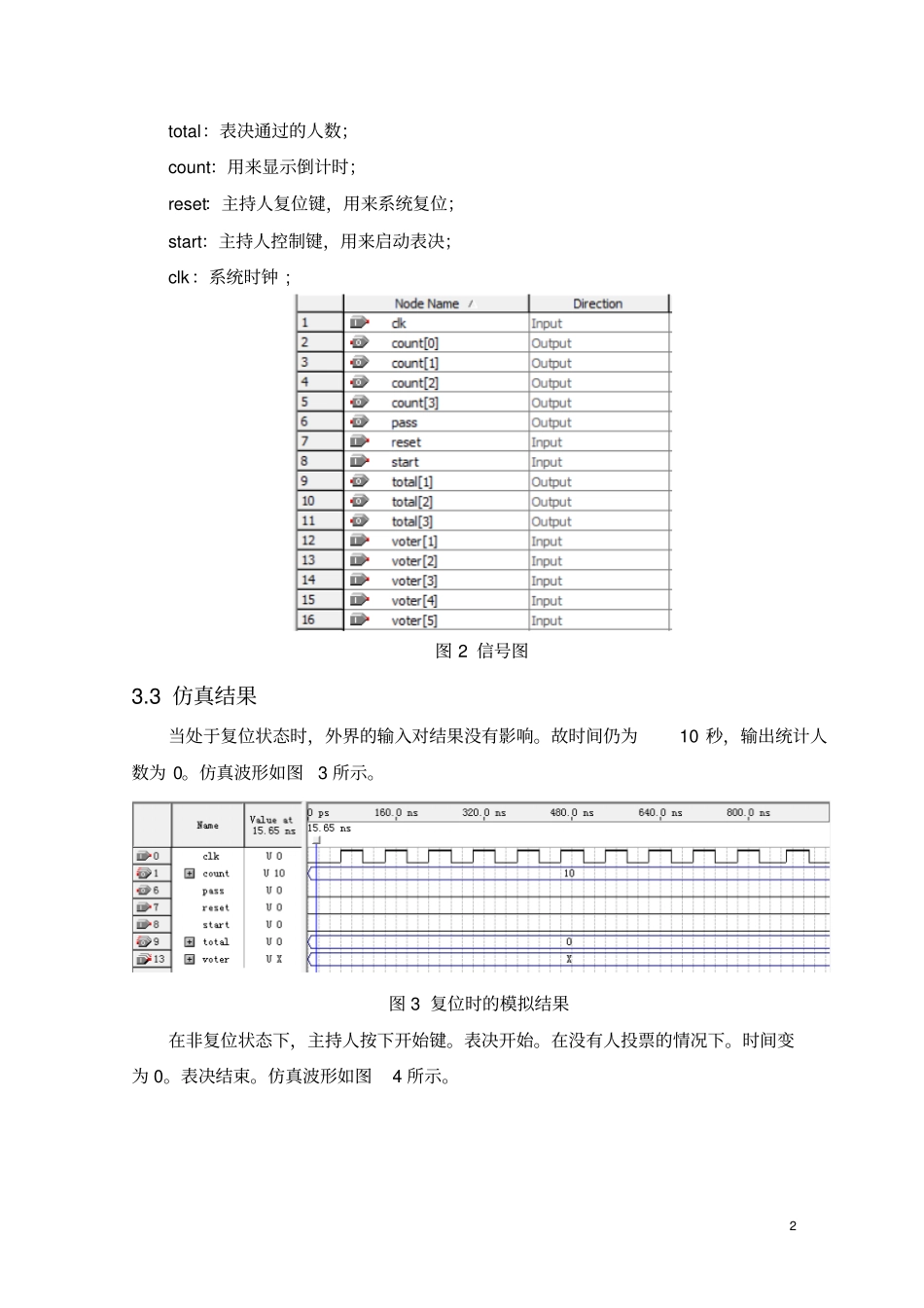

2信号表voter:一维数组voter用来表示五位表决者;pass:表决最终是否通过(‘1’为“通过”,‘0’为“未通过”);2total:表决通过的人数;count:用来显示倒计时;reset:主持人复位键,用来系统复位;start:主持人控制键,用来启动表决;clk:系统时钟;图2信号图3

3仿真结果当处于复位状态时,外界的输入对结果没有影响

故时间仍为10秒,输出统计人数为0

仿真波形如图3所示

图3复位时的模拟结果在非复位状态下,主持人按下开始键

在没有人投票的情况下

仿真波形如图4所示

3图4无人赞成时的模拟结果在非复位状态下,主持人按下开始键

当超出表决时间时才进行表决,此表决无效

仿真波形如图5所示

图5规定时间外的模拟结果在非复位状态下,主持人按下开始键

在规定时间内只有两人赞同,仿真波形如图6所示

图6两人赞成时的结果4在非复位状态下,主持人按下开始键

在规定时间内只有三人赞同,仿真波形如图7所示

图7三人赞成时的结果在非复位状态下,主持人按下开始键

在规定时间内只有四人赞同,仿真波形如图8所示

图7四人赞成时的结果该实验是一个具有计时功能的五人表决器,时