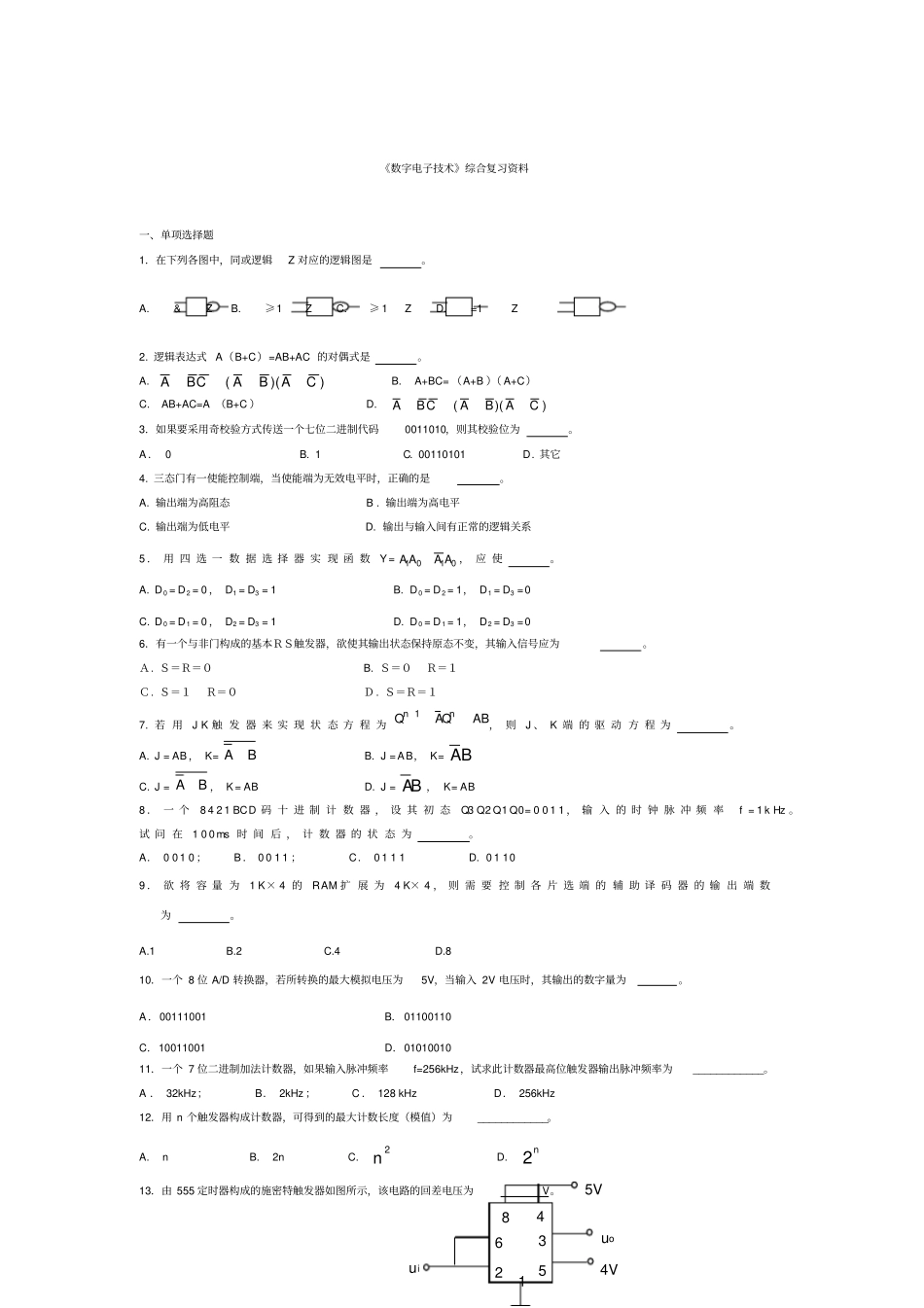

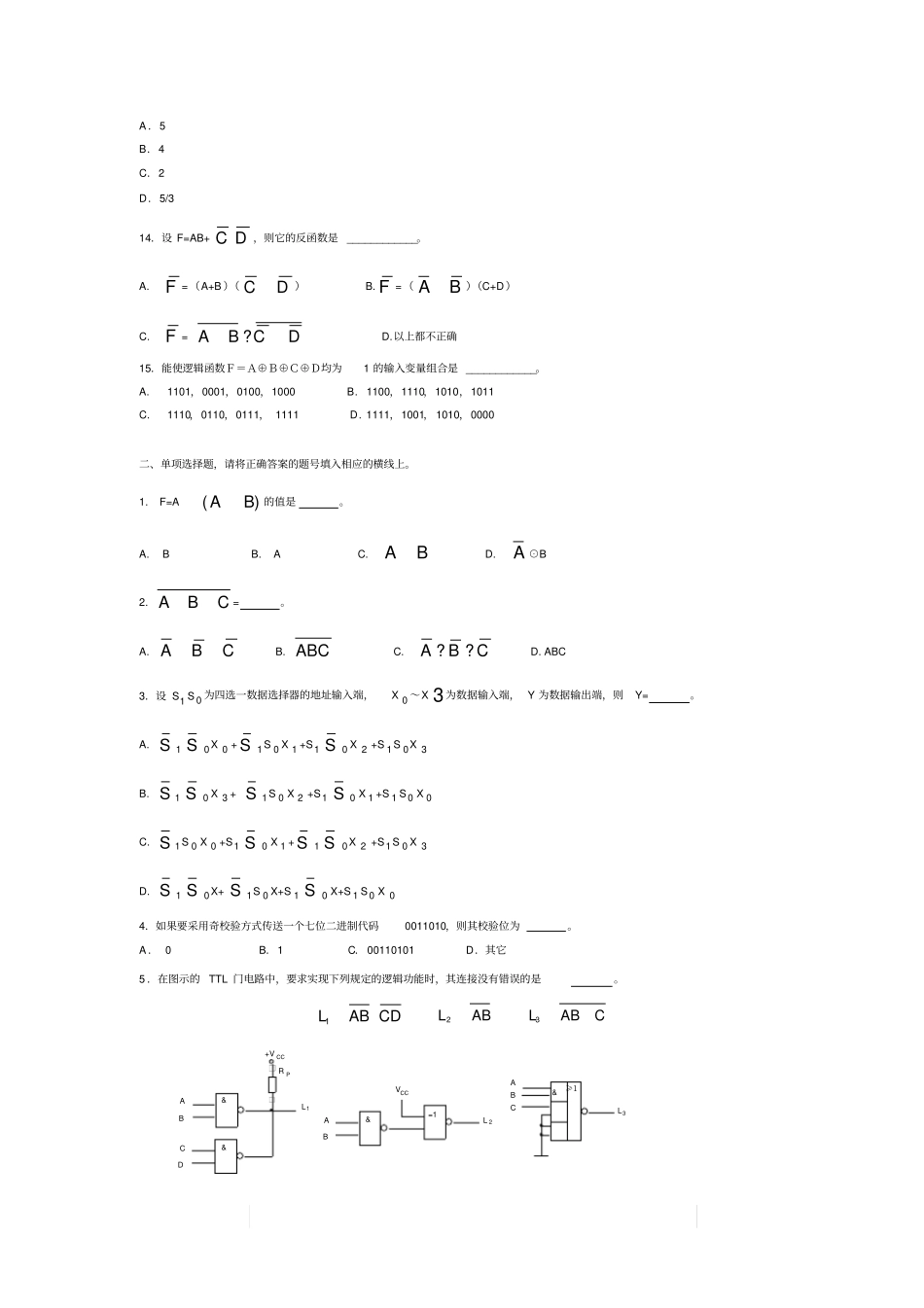

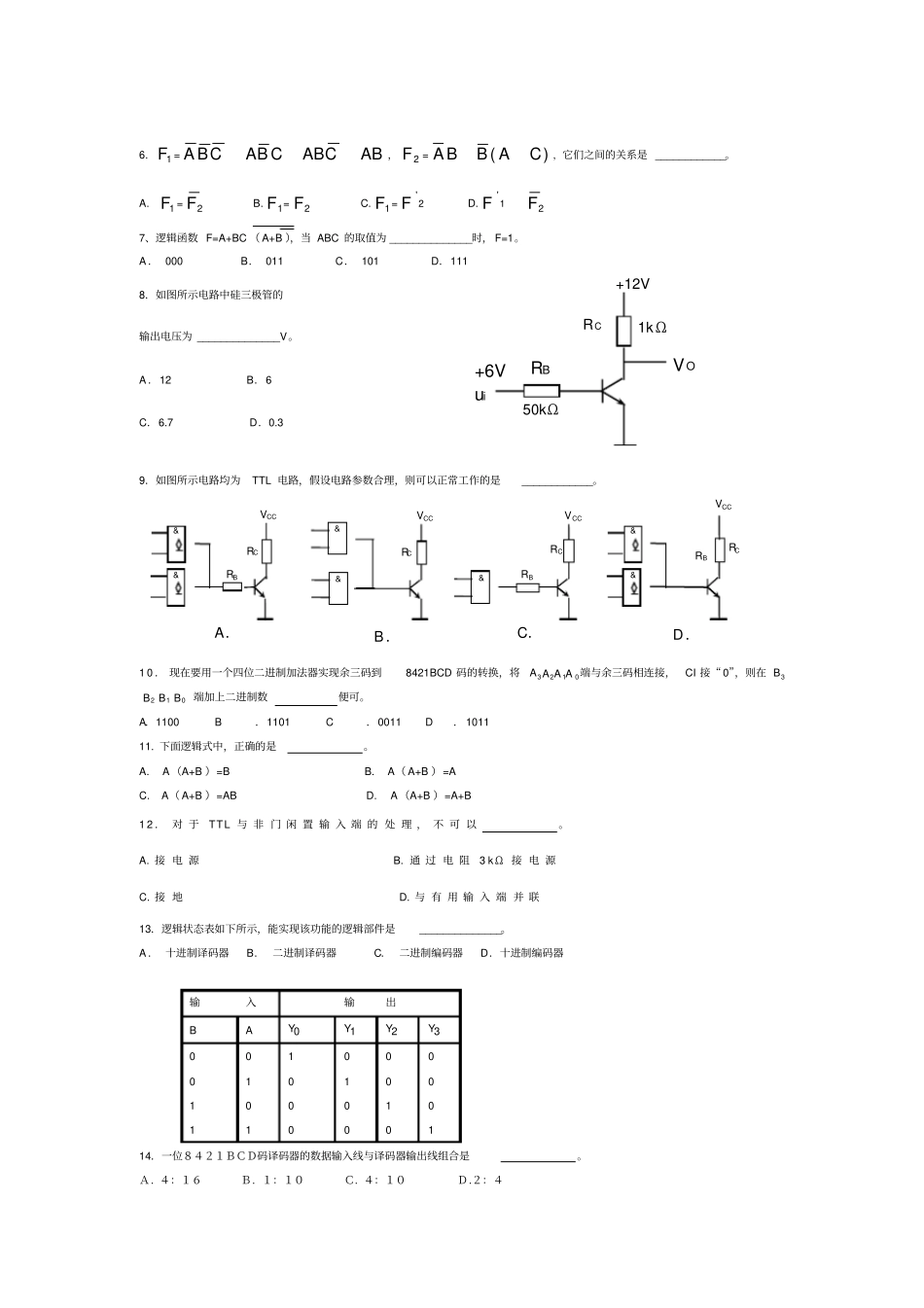

《数字电子技术》综合复习资料一、单项选择题1.在下列各图中,同或逻辑Z对应的逻辑图是。A.&ZB.≥1ZC.≥1ZD.=1Z2.逻辑表达式A(B+C)=AB+AC的对偶式是。A.))((CABACBAB.A+BC=(A+B)(A+C)C.AB+AC=A(B+C)D.))((CABACBA3.如果要采用奇校验方式传送一个七位二进制代码0011010,则其校验位为。A.0B.1C.00110101D.其它4.三态门有一使能控制端,当使能端为无效电平时,正确的是。A.输出端为高阻态B.输出端为高电平C.输出端为低电平D.输出与输入间有正常的逻辑关系5.用四选一数据选择器实现函数Y=0101AAAA,应使。A.D0=D2=0,D1=D3=1B.D0=D2=1,D1=D3=0C.D0=D1=0,D2=D3=1D.D0=D1=1,D2=D3=06.有一个与非门构成的基本RS触发器,欲使其输出状态保持原态不变,其输入信号应为。A.S=R=0B.S=0R=1C.S=1R=0D.S=R=17.若用JK触发器来实现状态方程为ABQAQn1n,则J、K端的驱动方程为。A.J=AB,K=BAB.J=AB,K=BAC.J=BA,K=ABD.J=BA,K=AB8.一个8421BCD码十进制计数器,设其初态Q3Q2Q1Q0=0011,输入的时钟脉冲频率f=1kHz。试问在100ms时间后,计数器的状态为。A.0010;B.0011;C.0111D.01109.欲将容量为1K×4的RAM扩展为4K×4,则需要控制各片选端的辅助译码器的输出端数为。A.1B.2C.4D.810.一个8位A/D转换器,若所转换的最大模拟电压为5V,当输入2V电压时,其输出的数字量为。A.00111001B.01100110C.10011001D.0101001011.一个7位二进制加法计数器,如果输入脉冲频率f=256kHz,试求此计数器最高位触发器输出脉冲频率为____________。A.32kHz;B.2kHz;C.128kHzD.256kHz12.用n个触发器构成计数器,可得到的最大计数长度(模值)为____________。A.nB.2nC.2nD.n213.由555定时器构成的施密特触发器如图所示,该电路的回差电压为V。ui6215384uo4V5VA.5B.4C.2D.5/314.设F=AB+DC,则它的反函数是____________。A.F=(A+B)(DC)B.F=(BA)(C+D)C.F=DCBA?D.以上都不正确15.能使逻辑函数F=A⊕B⊕C⊕D均为1的输入变量组合是____________。A.1101,0001,0100,1000B.1100,1110,1010,1011C.1110,0110,0111,1111D.1111,1001,1010,0000二、单项选择题,请将正确答案的题号填入相应的横线上。1.F=A)(BA的值是。A.BB.AC.BAD.A⊙B2.CBA=。A.CBAB.ABCC.CBA??D.ABC3.设S1S0为四选一数据选择器的地址输入端,X0~X3为数据输入端,Y为数据输出端,则Y=。A.S1S0X0+S1S0X1+S1S0X2+S1S0X3B.S1S0X3+S1S0X2+S1S0X1+S1S0X0C.S1S0X0+S1S0X1+S1S0X2+S1S0X3D.S1S0X+S1S0X+S1S0X+S1S0X04.如果要采用奇校验方式传送一个七位二进制代码0011010,则其校验位为。A.0B.1C.00110101D.其它5.在图示的TTL门电路中,要求实现下列规定的逻辑功能时,其连接没有错误的是。CDABL1ABL2CABL3+V&RPCD&LCCBA1B&A=1VCCL2&L3CBA≥16.1F=ABCABCBACBA,2F=)(CABBA,它们之间的关系是____________。A.1F=2FB.1F=2FC.1F=2'FD.21'FF7、逻辑函数F=A+BC(A+B),当ABC的取值为______________时,F=1。A.000B.011C.101D.1118.如图所示电路中硅三极管的输出电压为______________V。A.12B.6C.6.7D.0.39.如图所示电路均为TTL电路,假设电路参数合理,则可以正常工作的是____________。10.现在要用一个四位二进制加法器实现余三码到8421BCD码的转换,将A3A2A1A0端与余三码相连接,CI接“0”,则在B3B2B1B0端加上二进制数便可。A.1100B.1101C.0011D.101111.下面逻辑式中,正确的是。A.A(A+B)=BB.A(A+B)=AC.A(A+B)=ABD.A(A+B)=A+B12.对于TTL与非门闲置输入端的处理,不可以。A.接电源B.通过电阻3kΩ接电源C.接地D.与有用输入端并联13.逻辑状态表如下所示,能实现该功能的逻辑部件是______________。A.十进制译码器B.二进制译码器C.二进制编码器D.十进制编码器输入输出BAY0Y1Y2Y300100001010010001011000114.一位8421BCD码译码器的数据输入线与译码器输出线组合是。A.4:16B.1:10C.4:10D.2:4+12VRCRB+6VuiVO1kΩ50kΩVCCRCRBA.&&RCVCCRBC.&D.VCCRCRB&&VCCRCB.&&15.下列表达式对应的电路不存在竞争冒险的是。A.CBB...