实验五数据选择器及其应用[实验目的]1、掌握中规模集成数据选择器的逻辑功能及使用方法

2、学习用数据选择器构成组合逻辑电路的方法

[实验原理]数据选择器又叫“多路开关”

数据选择器在地址码(或叫选择控制)电位的控制下,从几个数据输入中选择一个并将其送到一个公共的输出端

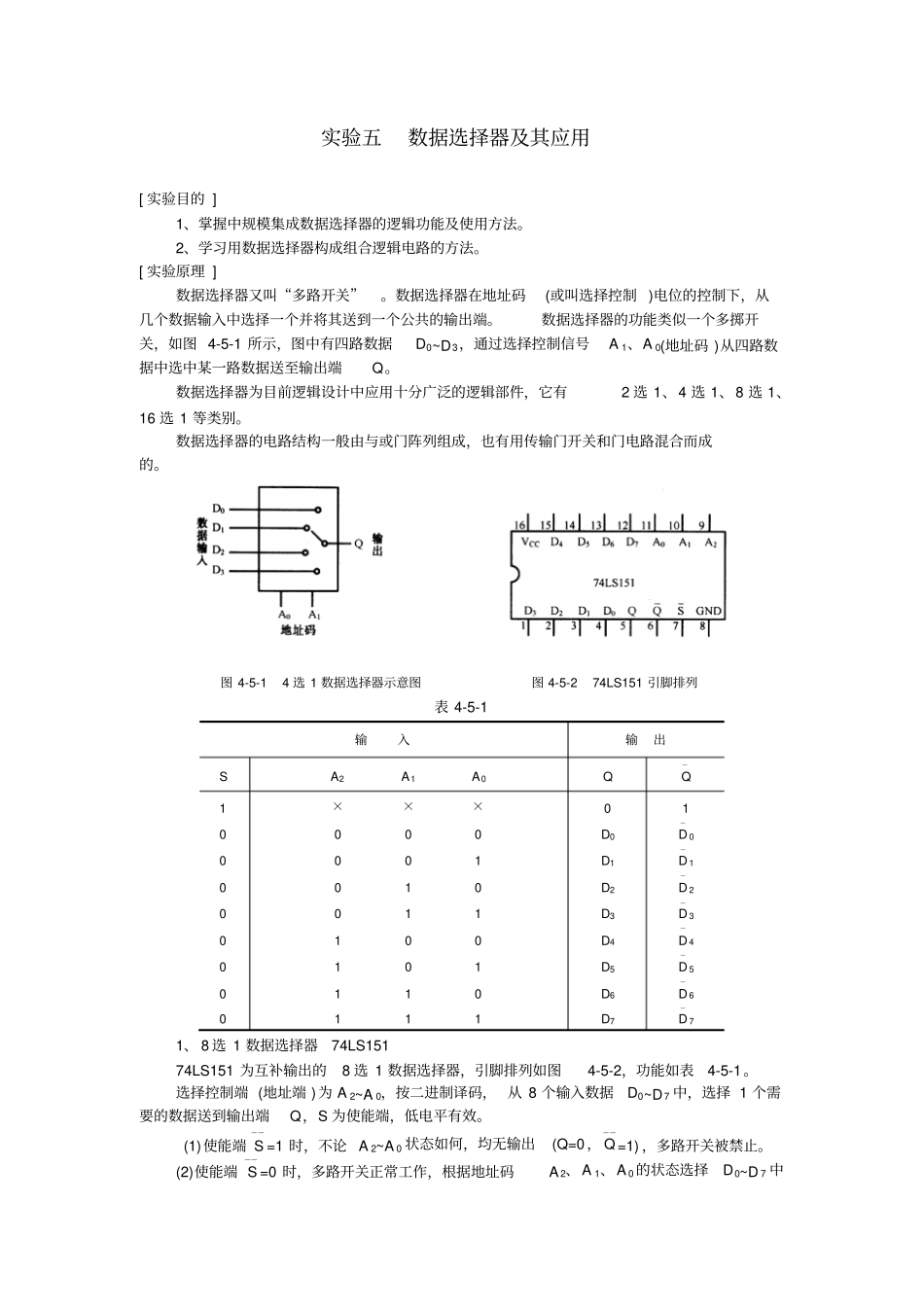

数据选择器的功能类似一个多掷开关,如图4-5-1所示,图中有四路数据D0~D3,通过选择控制信号A1、A0(地址码)从四路数据中选中某一路数据送至输出端Q

数据选择器为目前逻辑设计中应用十分广泛的逻辑部件,它有2选1、4选1、8选1、16选1等类别

数据选择器的电路结构一般由与或门阵列组成,也有用传输门开关和门电路混合而成的

图4-5-14选1数据选择器示意图图4-5-274LS151引脚排列表4-5-1输入输出SA2A1A0QQ—100000000×××0000010100111001011101110D0D1D2D3D4D5D6D71D—0D—1D—2D—3D—4D—5D—6D—71、8选1数据选择器74LS15174LS151为互补输出的8选1数据选择器,引脚排列如图4-5-2,功能如表4-5-1

选择控制端(地址端)为A2~A0,按二进制译码,从8个输入数据D0~D7中,选择1个需要的数据送到输出端Q,S为使能端,低电平有效

(1)使能端S——=1时,不论A2~A0状态如何,均无输出(Q=0,Q——=1),多路开关被禁止

(2)使能端S——=0时,多路开关正常工作,根据地址码A2、A1、A0的状态选择D0~D7中某一个通道的数据输送到输出端Q

如:A2A1A0=000,则选择D0数据到输出端,即Q=0

如:A2A1A0=001,则选择D1数据到输出端,即Q=D1,其余类推

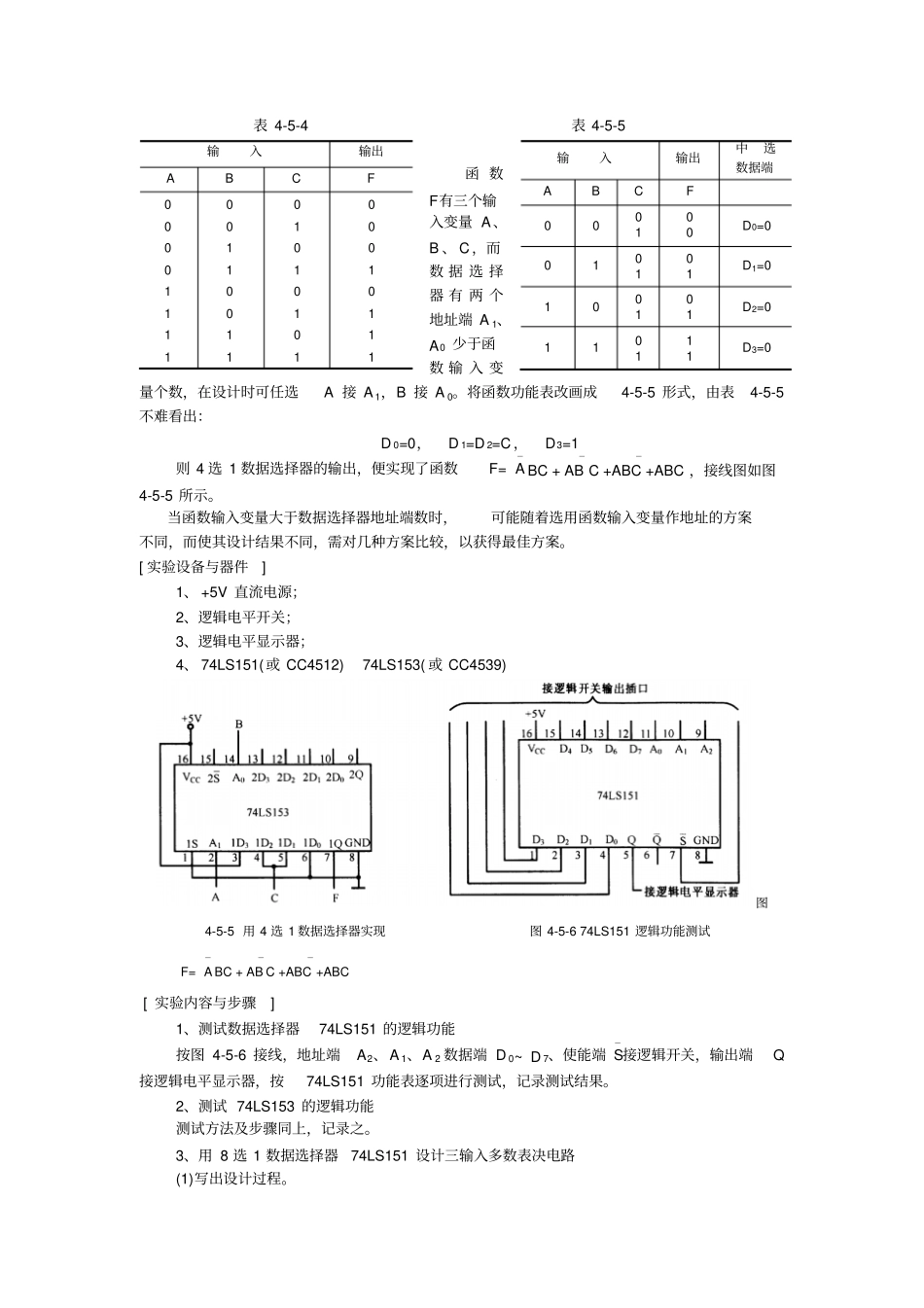

2、双四选一数据选择器74LS153所谓双4选1数据选择器就是在一块集成芯片上有两个4选1数据选择器

74LS153的引脚排列如图