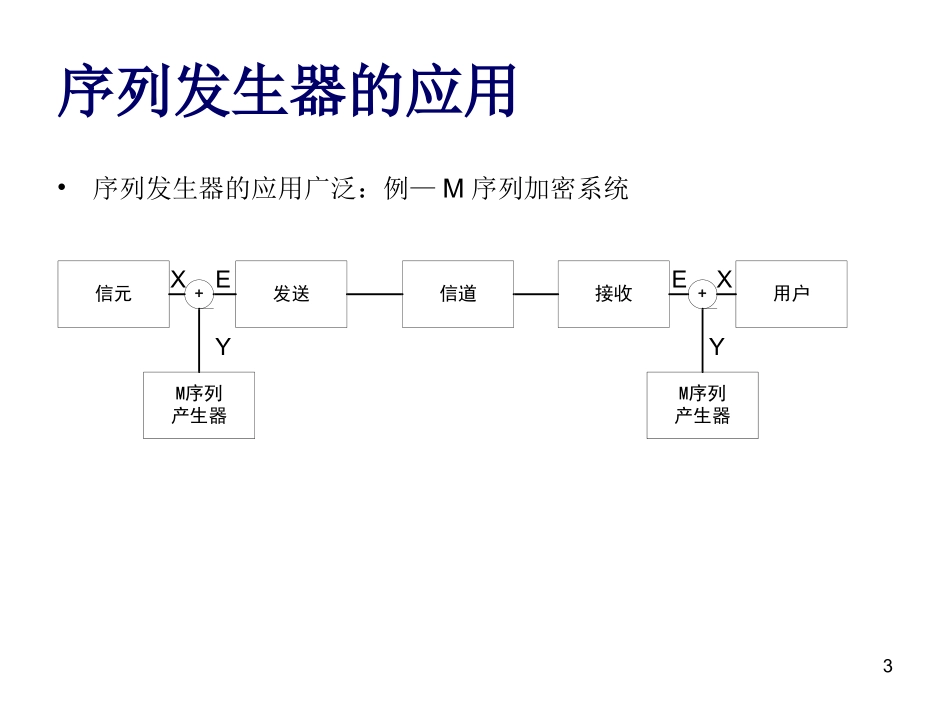

1序列发生器设计2序列发生器•数字系统中,常需要串行周期性信号;•序列信号:按照特定顺序排列的串行数字信号;•序列信号发生器:生成某个特定规则下的序列信号的电路。3序列发生器的应用•序列发生器的应用广泛:例—M序列加密系统信元发送信道接收用户M序列产生器M序列产生器++XEYEYX4序列发生器的设计•序列信号发生器的设计方法:–根据给定的序列信号设计序列信号生成电路;–根据序列长度M,选择长度为M的序列信号;•序列信号发生器的结构:–移存型序列信号发生器;–计数型信号发生器;5移存型序列信号发生器•以移位寄存器作为主要存储部件;•将给定的长度为M的序列信号,按移存规律,组成M个状态组合,完成状态转移;•求出移位寄存器的串行输入激励函数,即可构成该序列信号的产生电路。•例:设计产生序列信号为11000的发生器6移存型序列信号发生器序号Q3Q2Q101101100200030014011状态转移表1100000011000111110101017移存型序列信号发生器•第一步:根据要求列真值表和状态图•第二步:根据真值表画卡诺图,求次态方程;•Q1n+1=not(Q3n.Q2n)•第三步:检查系统能否自启动;•第四步:确定触发器类型和数目;•第五步:确定逻辑电路图;8移存型序列信号发生器entityshiftxuilieisport(clk:inbit;d:inbit;set:inbit;reset:inbit;q:outbit;nq:outbit);endshiftxuilie;architecturebehavioralofshiftxuilieiscomponentDtriggerport(clk:inbit;d:inbit;set:inbit;reset:inbit;q:outbit;nq:outbit);endcomponent;signalt0,t00,t01,t1,t10,t11,t2,t20,t21,t3,t4,t5:bit:='0';beginU1:Dtriggerportmap(clk,t0,set,reset,t00,t01);U2:Dtriggerportmap(clk,t00,set,reset,t10,t11);U3:Dtriggerportmap(clk,t10,set,reset,t20,t21);t0<=t11andt21;q<=t20;nq<=nott20;endbehavioral;9序列发生器的功能仿真波形的建立10计数型序列信号发生器•以同步计数器为基础;•例:设计产生序列信号为1111000100的发生器;•序列长度M=10,选用一个模10的同步计数器11计数型序列信号发生器Q3Q2Q1Q0F00001000110010100111010000101001100011111000010010F=(not(Q3)andnot(Q2))or(Q1andQ0)12计数型序列信号发生器libraryieee;useieee.std_logic_1164.all;useieee.std_logic_arith.all;useieee.std_logic_unsigned.all;entitycounterxuelieisport(clk:instd_logic;clr:instd_logic;f:outstd_logic;q:outstd_logic_vector(3downto0));endcounterxuelie;architecturebehavioralofcounterxuelieissignalq0:std_logic_vector(3downto0);signaltemp1,temp2,temp3:std_logic;beginprocess(clk,clr)beginif(clr='0')thenq0<="0000";elsif(clk'eventandclk='1')thenif(q0="1001")thenq0<="0000";elseq0<=q0+'1';endif;endif;endprocess;q<=q0;temp1<=(notq0(3))and(notq0(2));temp2<=q0(1)andq0(0);temp3<=(nottemp1)and(nottemp2);f<=nottemp3;endbehavioral;13计数型序列信号发生器14状态机实现序列信号发生器试用状态机的设计方法实现序列0110101发生器S2S1S0S6S3S4S5000111115状态机实现序列信号发生器architectureBehavioralofexam_stateistypestate_typeis(S0,s1,s2,s3,s4,s5,S6);signalstate:state_type;beginSYNC_PROC:process(CLK)beginif(CLK'eventandCLK='1')thencase(state)iswhenS0=>state<=S1;current_state<='0';whenS1=>state<=S2;current_state<='1';whenS2=>state<=S3;current_state<='1';whenS3=>state<=S4;current_state<='0';whenS4=>state<=S5;current_state<='1';whenS5=>state<=S6;current_state<='0';whenS6=>state<=S0;current_state<='1';whenothers=>state<=S1;endcase;ENDIF;endprocess;endBehavioral;16状态图——利用QuartusII软件