第6章CMOS组合逻辑门的设计CMOS组合逻辑门的设计

2本章重点•深入讨论CMOS逻辑系列——静态和动态、传输晶体管、无比和有比逻辑•优化逻辑门的面积、速度、能量或稳定性•低功耗高性能的电路设计技术CMOS组合逻辑门的设计

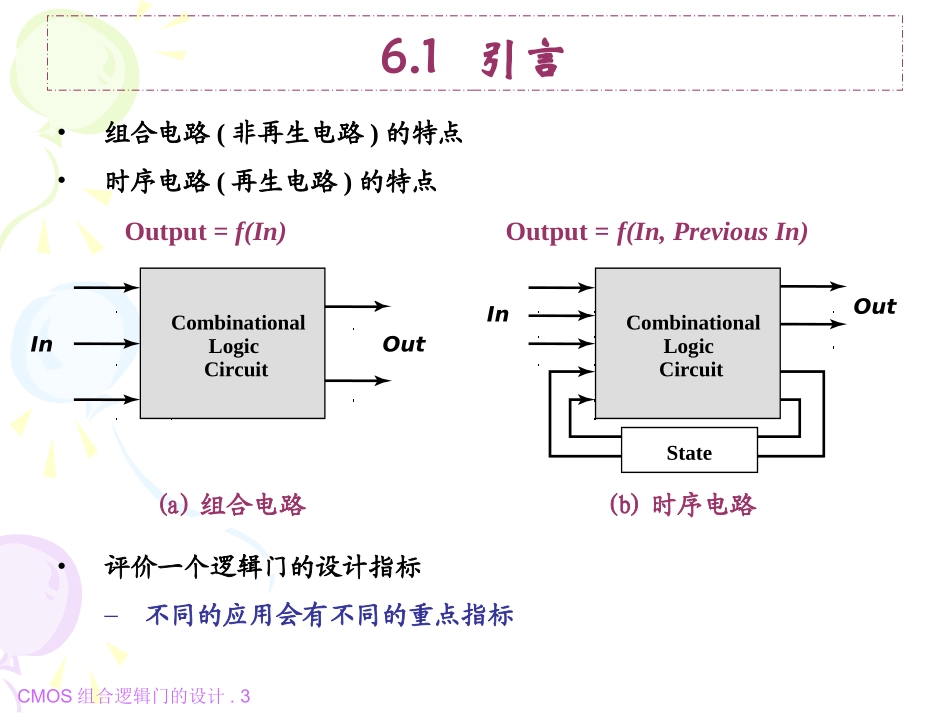

1引言•组合电路(非再生电路)的特点•时序电路(再生电路)的特点•评价一个逻辑门的设计指标–不同的应用会有不同的重点指标Output=f(In)Output=f(In,PreviousIn)CombinationalLogicCircuitOutInCombinationalLogicCircuitOutInState(a)组合电路(b)时序电路CMOS组合逻辑门的设计

2静态CMOS设计•静态CMOS–每一时刻每个门的输出通过一个低阻路径连到VDD或VSS上–同时在任何时候该门的输出即为该电路实现的布尔函数值•动态CMOS–把信号值暂时存放在高阻抗电路节点的电容上–所形成的门比较简单且比较快速–对噪声敏感程度增加•本节讨论的静态电路类型的设计:–互补CMOS–有比逻辑(伪NMOS和DCVSL)–传输管逻辑CMOS组合逻辑门的设计

1互补CMOS概念:•静态CMOS门是上拉网络(PUN)和下拉网络(PDN)的组合•PUN和PDN网络是以相互排斥的方式构成的•在稳定状态时输出节点总是一个低阻节点VDDF(In1,In2,…InN)In1In2InNIn1In2InNPUNPDN……由PMOS管构成上拉网络:每当F(In1,In2,…InN)=1时,它将提供一条在输出和VDD之间的通路由NMOS管构成下拉网络:每当F(In1,In2,…InN)=0时,它将提供一条在输出和GND之间的通路CMOS组合逻辑门的设计

6在构成PUN和PDN网络时应当记住以下几点:•晶体管可以看成是由其栅信号控制的开关•PDN由NMOS器件构成,而PUN由P