常用数字逻辑门电路的研究实验目的实验原理注意事项实验内容一、实验目的1.熟悉数字电路实验系统的正确使用方法;2

熟悉CMOS各种常用门电路的逻辑符号及逻辑功能;3

测量逻辑门电路的时延参数;二、实验原理1

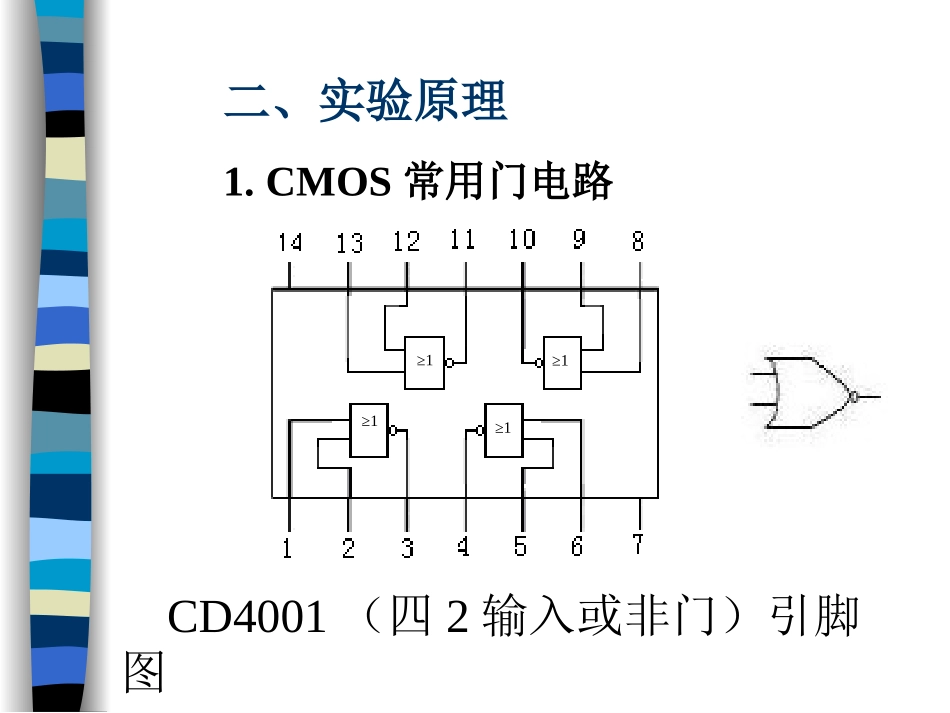

CMOS常用门电路CD4001(四2输入或非门)引脚图≥1≥1≥1≥1CD4011(四2输入与非门)引脚图&&&&CD4069(六反相器)引脚图111111CD4070(四异或门)引脚图=1=11=1=74LS125(三态门)引脚图1▽ENENENEN▽▽▽11174LS03(集电极开路门)引脚图&&&&数字逻辑箱三、实验内容1、对CD4070的逻辑功能的测试(1)用逻辑箱观测4070的逻辑功能并完成下表逻辑开关指示灯输入输出引脚()引脚()引脚()00011011(2)CD4070处于工作状态,并且使4070的1脚接高电平,2脚接频率为2KHZ的TTL信号

请用双踪示波器观察4070的2脚和3脚信号

画出这两个波形,标出信号周期,幅度和两信号相位关系

CD4069引脚图2、利用六反相器CD4069测量逻辑门电路的时延参数

将CD4069中的六个非门依次串联连接,在输入端输入250KHz的TTL信号,用双踪示波器测总的延时,计算每个门的平均传输延迟时间的tpd的值

HEF4069UBP器件资料中的时延参数输入输出测量逻辑门电路的时延参数若出现故障,检测时因遵循以下步骤:1、检查电源及各使能端

2、检查各集成块输入输出是否正常

(一级一级检查到集成块引脚,注意不要造成引脚短路

)四、注意事项五、思考题1、为什么异或门可用作非门,如何使用

为什么异或门是可控反相器

2、为什么CMOS集成门电路多余输入端不能悬空

下次实验预习题目实验三常用数字逻辑门输入输出特性测试1)空载时,CMOS器件的ViLmax,,ViHmin,,VoLmax,,VoHmin,各是多少

2)CMO