PCB 设计中降低开关噪声方法详述 并没有很多方法可以快速地对它的值进行评估

只有对封装和电源分配系统进行仔细的检查和详细的仿真才能得出一个较为合理结果

因为影响SSN 的因素实在是太多了,所以不可能要求得到一个精确的答案,而且要评估的几何体都是自然的三维结构,很大程度上还取决于单个芯片的封装(或者连接器)和管脚分布

由于这个问题的困难度,所以建议对SSN 的估算最好是通过仿真和测量的双重途径

而对于这种噪声源的控制,也只能遵循一些通用的规则

根据同步开关噪声的产生原因,我们可以从去耦电容的放置,驱动级,以及芯片封装等主要几个方面讨论如何在设计中减小SSN, 并分别对其进行仿真比较

在实际设计中,经常加去耦电容于PCB 和 MCM 系统抑制同步开关噪声

理论上若去耦电容足够大并靠近有源电路,则可消除SSN噪声,如图所示

但电容本身和通孔、电源板都有寄生电感,如果所有的电感之和远大于实际电源总线的电感,则不管去耦电容多大,也没有去耦效果

如两电感值相等,则即使加更大的电容,去耦效率也仅为一半或更低

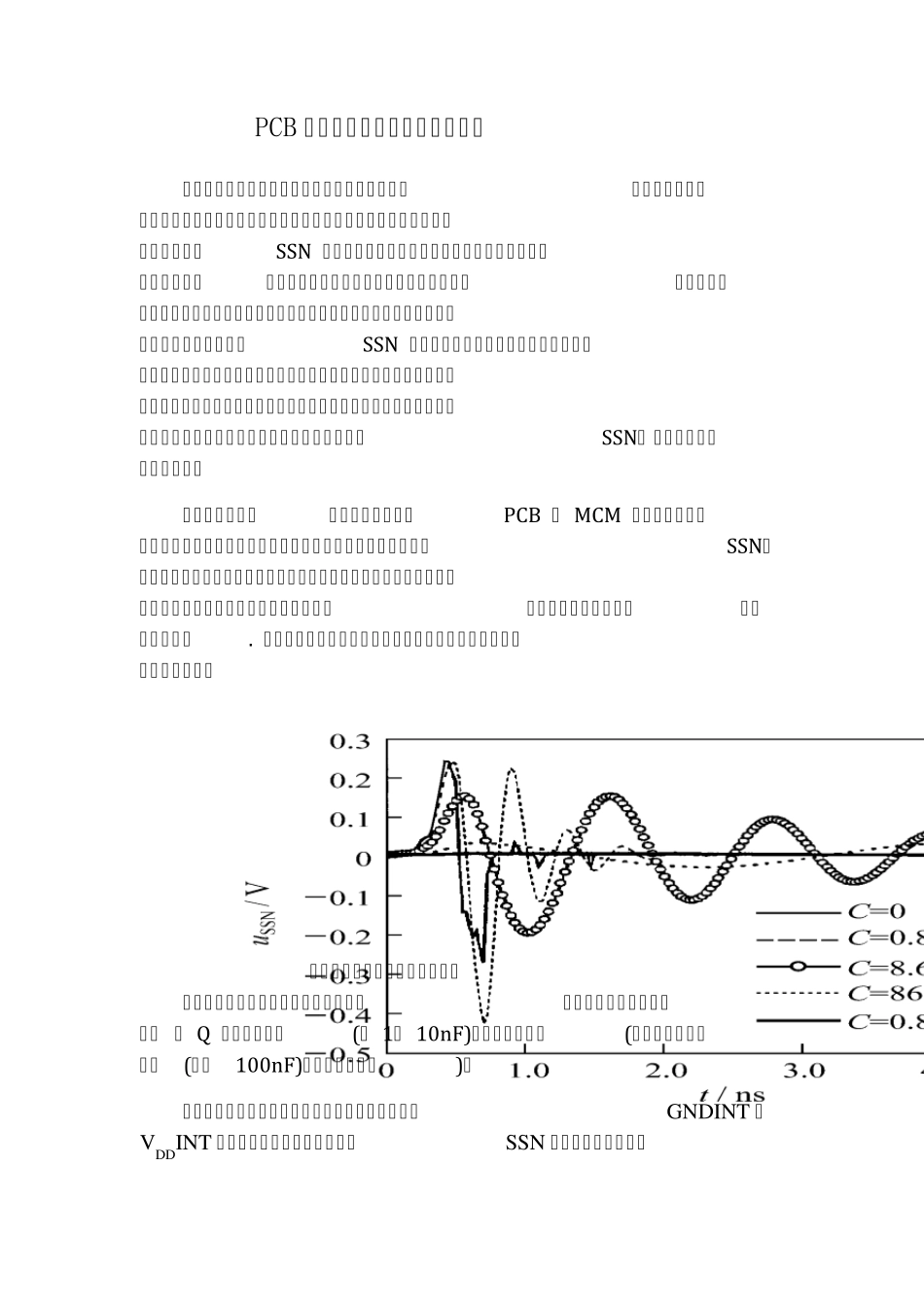

不同去耦电容下的同步开关噪声 因此,为了有效地抑制同步开关噪声, 倾向使用自激频率比较高、 高 Q 值的中等电容(约 1~ 10nF)分布于整个模块(因为大表面封装电容(如≥100nF)通常寄生电感大)

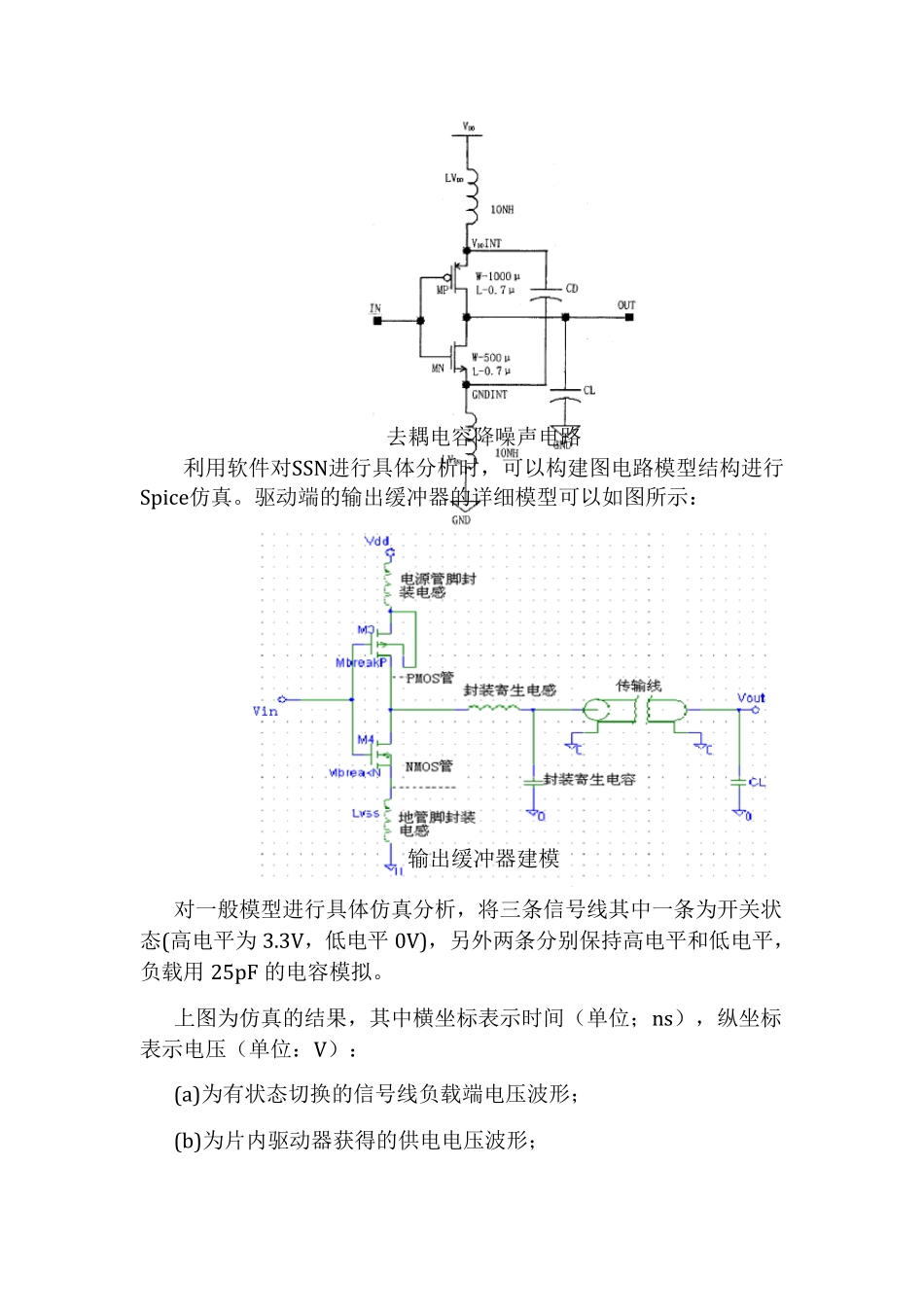

在电路设计中可通过在芯片内部加去耦电容(即在GNDINT 与V DDINT 之间加去耦电容)的办法减小SSN 的作用,如图所示: 去耦电容降噪声电路 利用软件对SSN进行具体分析时,可以构建图电路模型结构进行Spice仿真

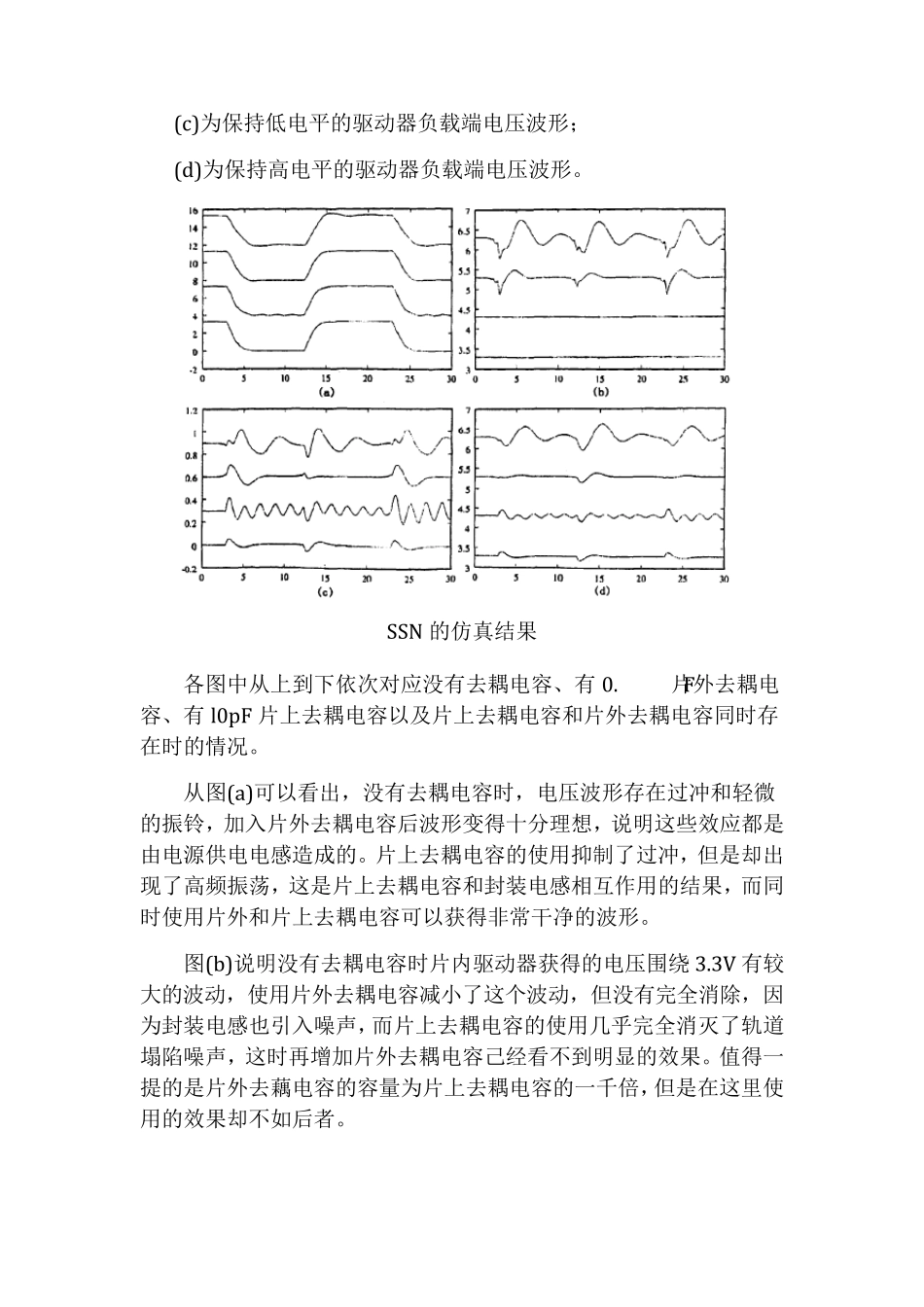

驱动端的输出缓冲器的详细模型可以如图所示: 输出缓冲器建模 对一般模型进行具体仿真分析,将三条信号线其中一条为开关状态(高电平为 3

3V,低电平 0V),另外两条分别保持高电平和低电平,负载用25pF 的电容模拟

上图为仿真的结果,其中横坐标表示时间