AmlogicDDR调试指南目的:本指南主要用来指导客户进行AmlogicDDR12nm芯片的调试,让客户通过调整timing

c,就能明确DDR的配置,确保能够顺利跑起来,同时进行DDR的测试

注:所有timing

c的调试,都是在确认硬件焊接正常、电源供电正常的基础上进行调试

一、DDR调试1、LPDDR3/4dq_remapdq_remap会影响DDR的training,必须正确设置

原则是lane0-lane3的组内排序,需要和原理图的对应上,如下图timing

c的dq_remap需要对应到原理图上LPDDR3/4的信号顺序,lane0-4顺序列到dq_remap上

Note:DDR3/DDR4部分只需要确认各个lane对应的DQS\DQM没有接错即可

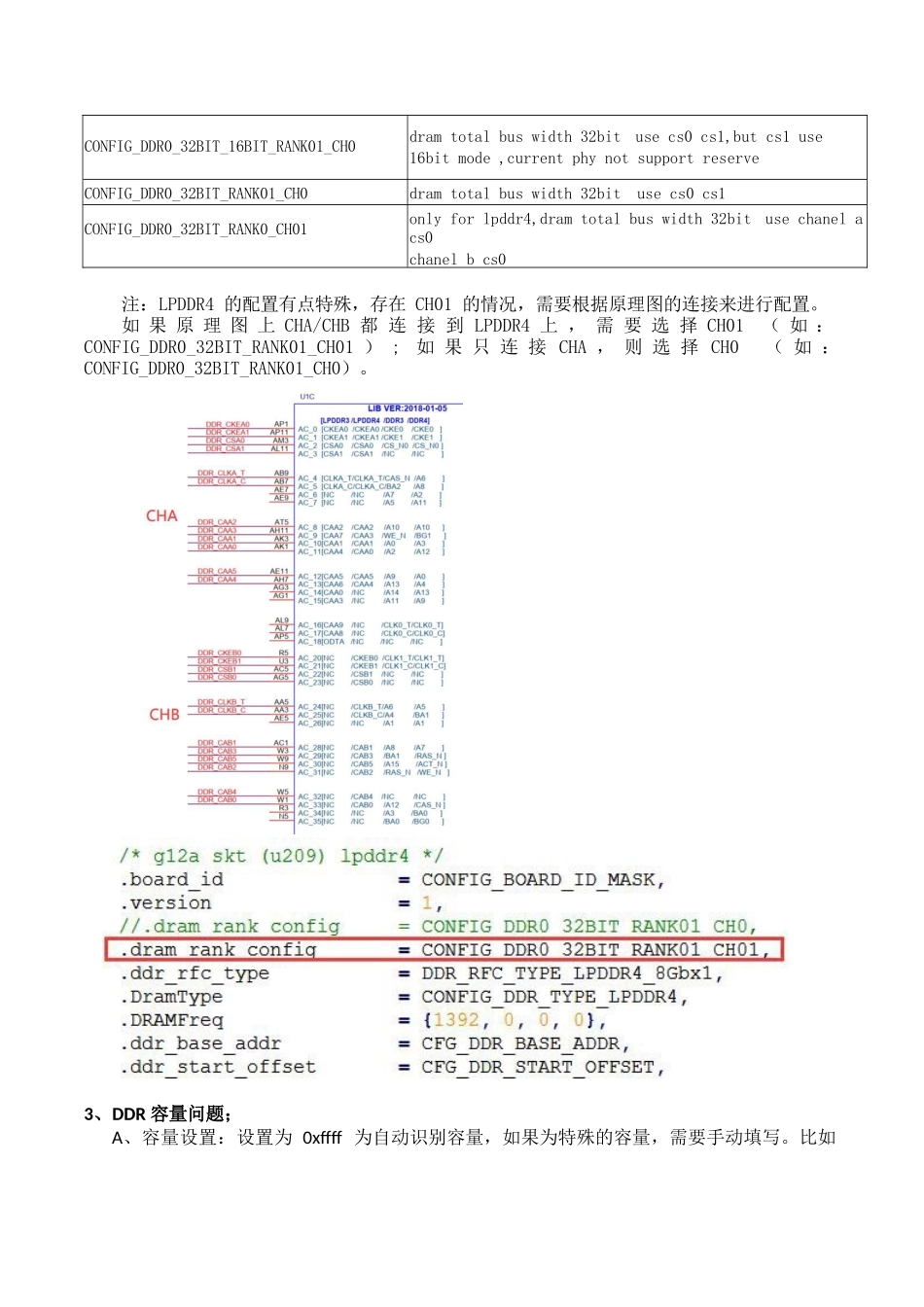

2、dram_rank_config的配置CONFIG_DDR0_32BIT_RANK01_CH0中的ch0对应SOC的DDRDQ信号,32bit的DQ对应只有ch0,RANK01在原理图上对应DDR_CS0和DDR_CS1的连接情况,如果CS0/CS1都连接,使用RANK01,否则使用RANK0

默认系统都用32bit,如果只有16bit的,请选择16bit

ConfigdetailCONFIG_DDR0_16BIT_CH0dramtotalbuswidth16bitonlyusecs0CONFIG_DDR0_16BIT_RANK01_CH0dramtotalbuswidth16bitusecs0cs1CONFIG_DDR0_32BIT_RANK0_CH0dramtotalbuswidth32bitusecs0CONFIG_DDR0_32BIT_RANK01_CH01onlyforlpddr4,dramtotalbuswidth32bitusechanelacs0cs1chanelbcs0cs1CONFIG_DD