25/1/18Chapt3组合逻辑电路的分析与设计第三章组合逻辑电路的分析与设计[教学要求]1

掌握逻辑代数的三种基本运算、三项基本定理、基本公式和常用公式;2

掌握逻辑函数的公式化简法和卡诺图化简法;3

了解最小项、最大项、约束项的概念及其在逻辑函数化简中的应用;4

掌握组合逻辑电路的分析与设计方法;5

了解组合电路中的竞争与冒险现象、产生原因及消除方法

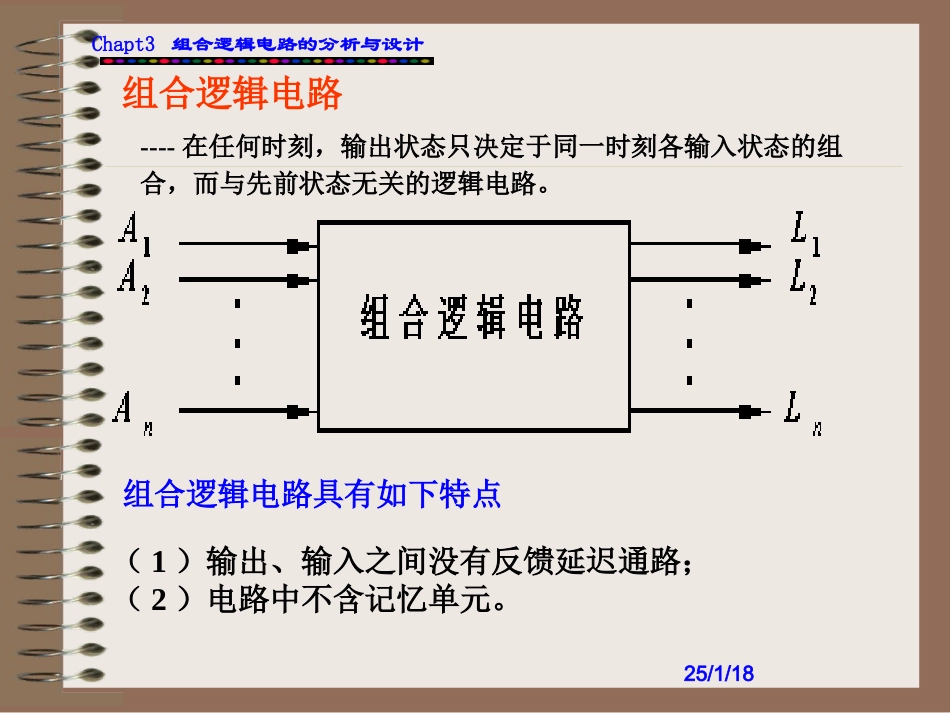

25/1/18Chapt3组合逻辑电路的分析与设计组合逻辑电路----在任何时刻,输出状态只决定于同一时刻各输入状态的组合,而与先前状态无关的逻辑电路

组合逻辑电路具有如下特点(1)输出、输入之间没有反馈延迟通路;(2)电路中不含记忆单元

25/1/18Chapt3组合逻辑电路的分析与设计3

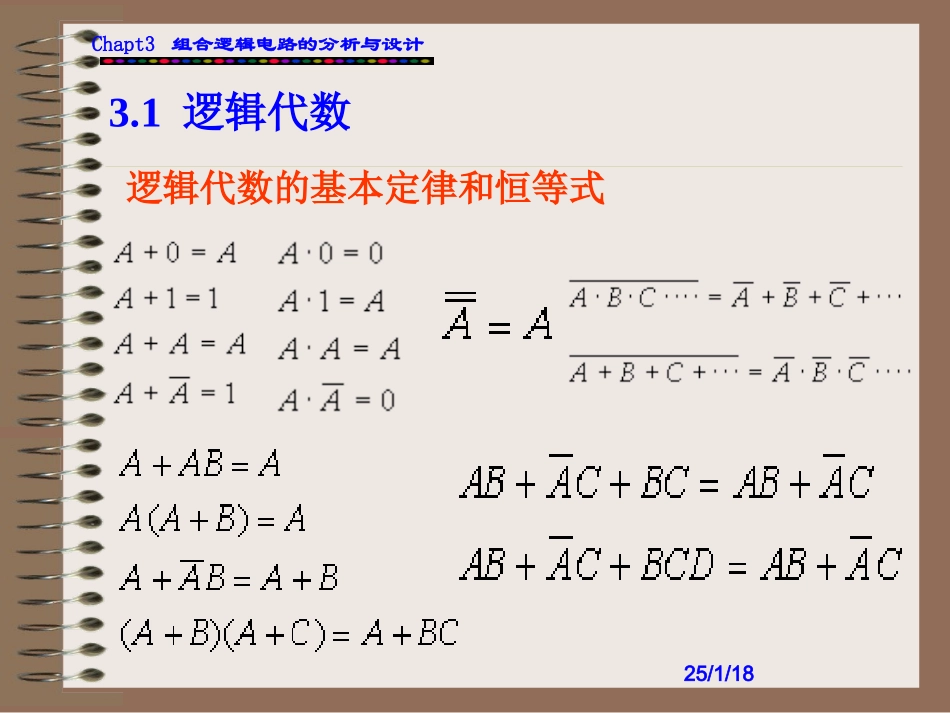

1逻辑代数逻辑代数的基本定律和恒等式25/1/18Chapt3组合逻辑电路的分析与设计25/1/18Chapt3组合逻辑电路的分析与设计1

代入规则:在任何一个逻辑等式中,如果将等式两边出现的某变量A,都用一个函数代替,则等式依然成立

反演规则:求一个逻辑函数L的非函数时,可以将L中的与(·)换成或(+),或(+)换成与(·);再将原变量换为非变量(如A换成),非变量换为原变量;并将1换成0,0换成1;那么所得的逻辑函数式就是

注意事项:1)保持原来的运算优先顺序

2)对于反变量以外的非号应保留不变

对偶规则:如把L中的与(·)换成或(+),或(+)换成与(·);1换成0,0换成1,那么就得到一个新的逻辑函数,这就是L的对偶式,记作(L')

变换时仍需注意保持原式中先“与”后“或”的顺序

ALL三种规则:25/1/18Chapt3组合逻辑电路的分析与设计逻辑函数的代数变换与化简法1

逻辑函数的变换一个特定的逻辑问题,对应的真值表是唯一的,但实现它的电路多种多样

逻辑函数的化简:1)最简与或表达式有以下两个特点: