时钟的抖动测量与分析 时钟抖动的分类与定义 时钟抖动通常分为时间间隔误差(Time Interv al Error,简称TIE),周期抖动(Period Jitter)和相邻周期抖动(cy cle to cy cle jitter)三种抖动

TIE 又称为phase jitter,是信号在电平转换时,其边沿与理想时间位置的偏移量

理想时间位置可以从待测试时钟中恢复,或来自于其他参考时钟

Period Jitter 是多个周期内对时钟周期的变化进行统计与测量的结果

Cy cle to cy cle jitter 是时钟相邻周期的周期差值进行统计与测量的结果

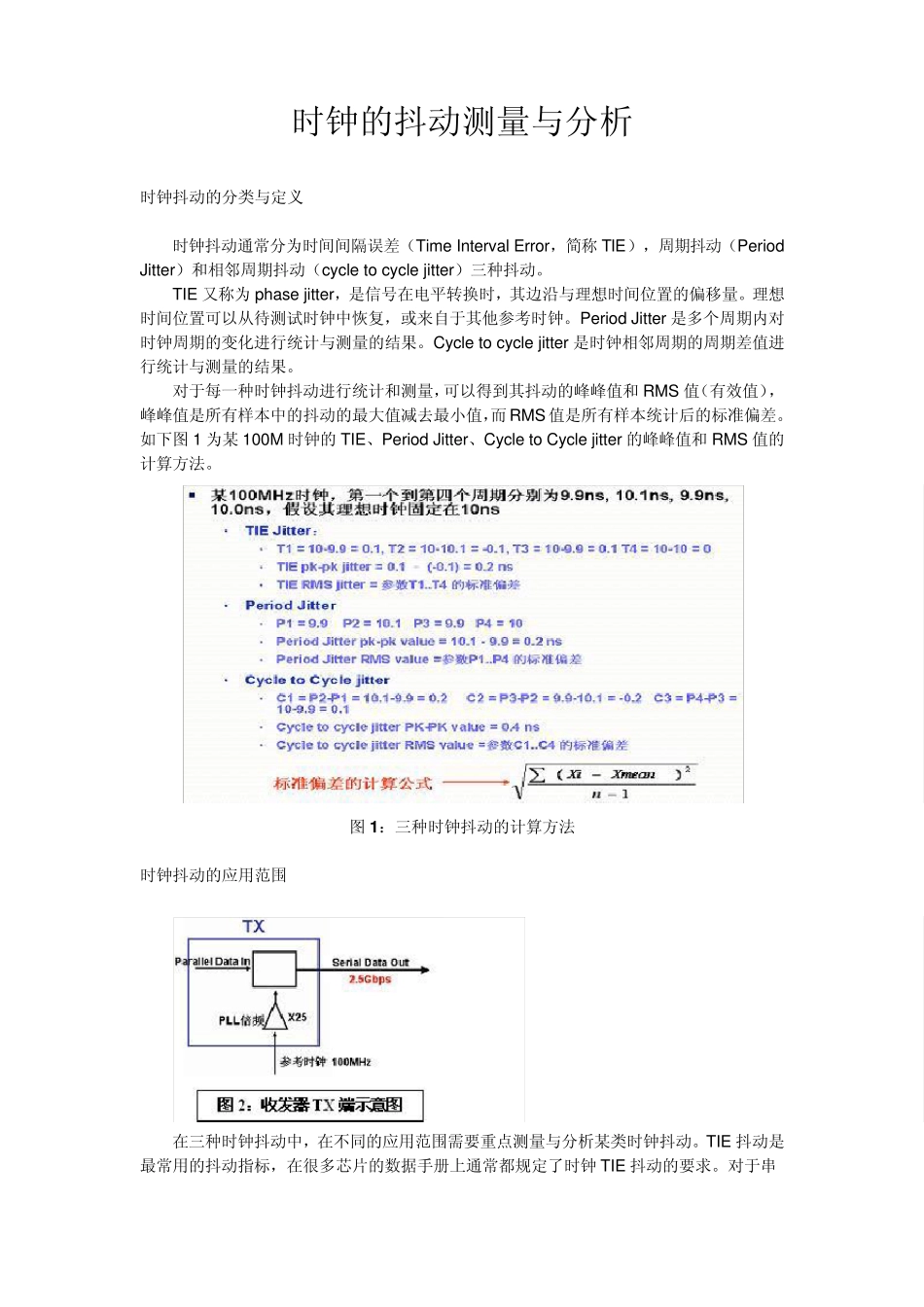

对于每一种时钟抖动进行统计和测量,可以得到其抖动的峰峰值和RMS 值(有效值),峰峰值是所有样本中的抖动的最大值减去最小值,而RMS 值是所有样本统计后的标准偏差

如下图1 为某100M 时钟的TIE、Period Jitter、Cy cle to Cy cle jitter 的峰峰值和RMS 值的计算方法

图1 :三种时钟抖动的计算方法 时钟抖动的应用范围 在三种时钟抖动中,在不同的应用范围需要重点测量与分析某类时钟抖动

TIE 抖动是最常用的抖动指标,在很多芯片的数据手册上通常都规定了时钟TIE 抖动的要求

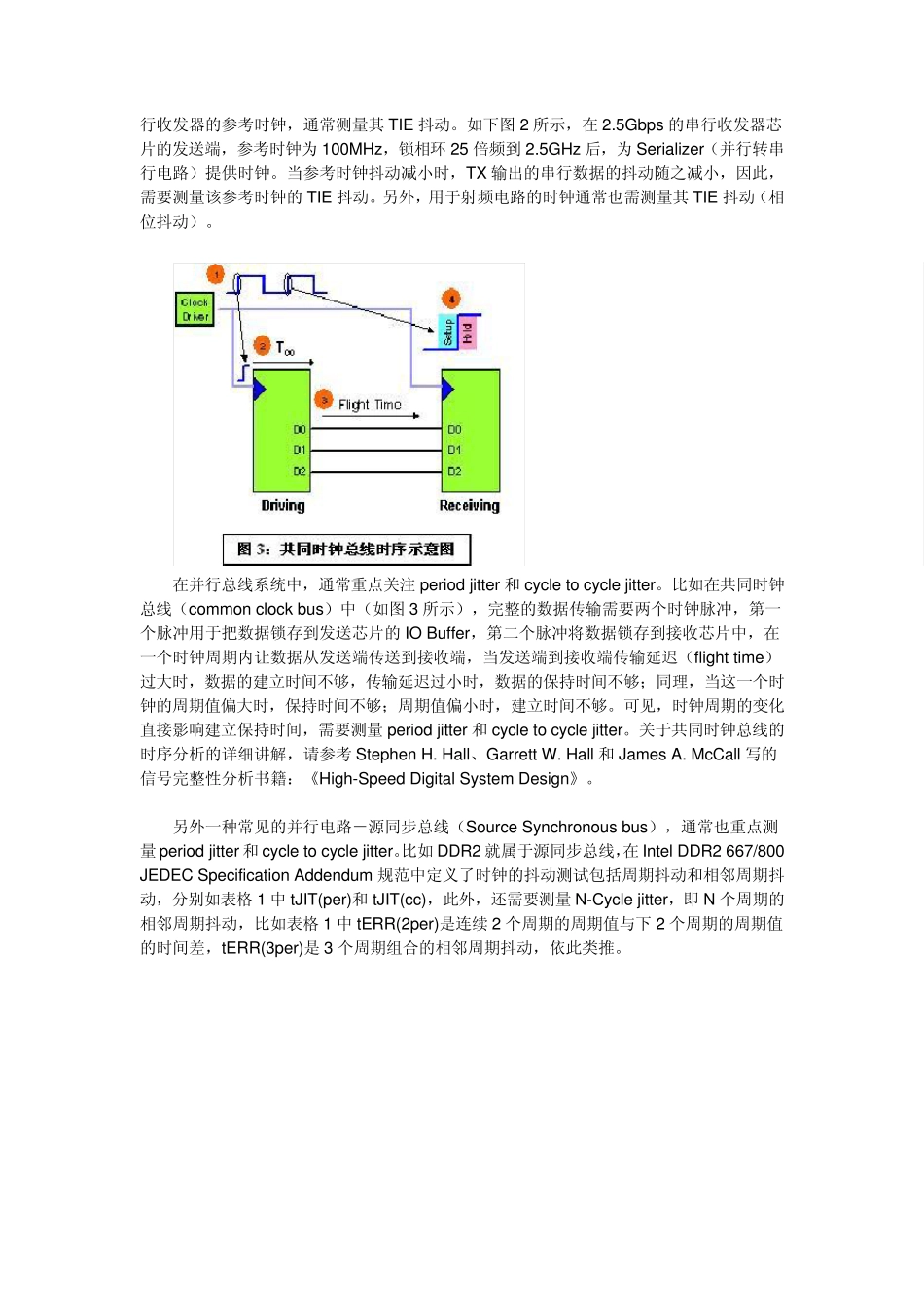

对于串行收发器的参考时钟,通常测量其 TIE 抖动

如下图 2 所示,在 2

5Gbps 的串行收发器芯片的发送端,参考时钟为 100MHz,锁相环 25 倍频到 2

5GHz 后,为 Serializer(并行转串行电路)提供时钟

当参考时钟抖动减小时,TX 输出的串行数据的抖动随之减小,因此,需要测量该参考时钟的 TIE 抖动

另外,用于射频电路的时钟通常也需测量其 TIE 抖动(相位抖动)

在并行总线系统中,通常重点关注 period jitter 和 cycle to cycle jitter