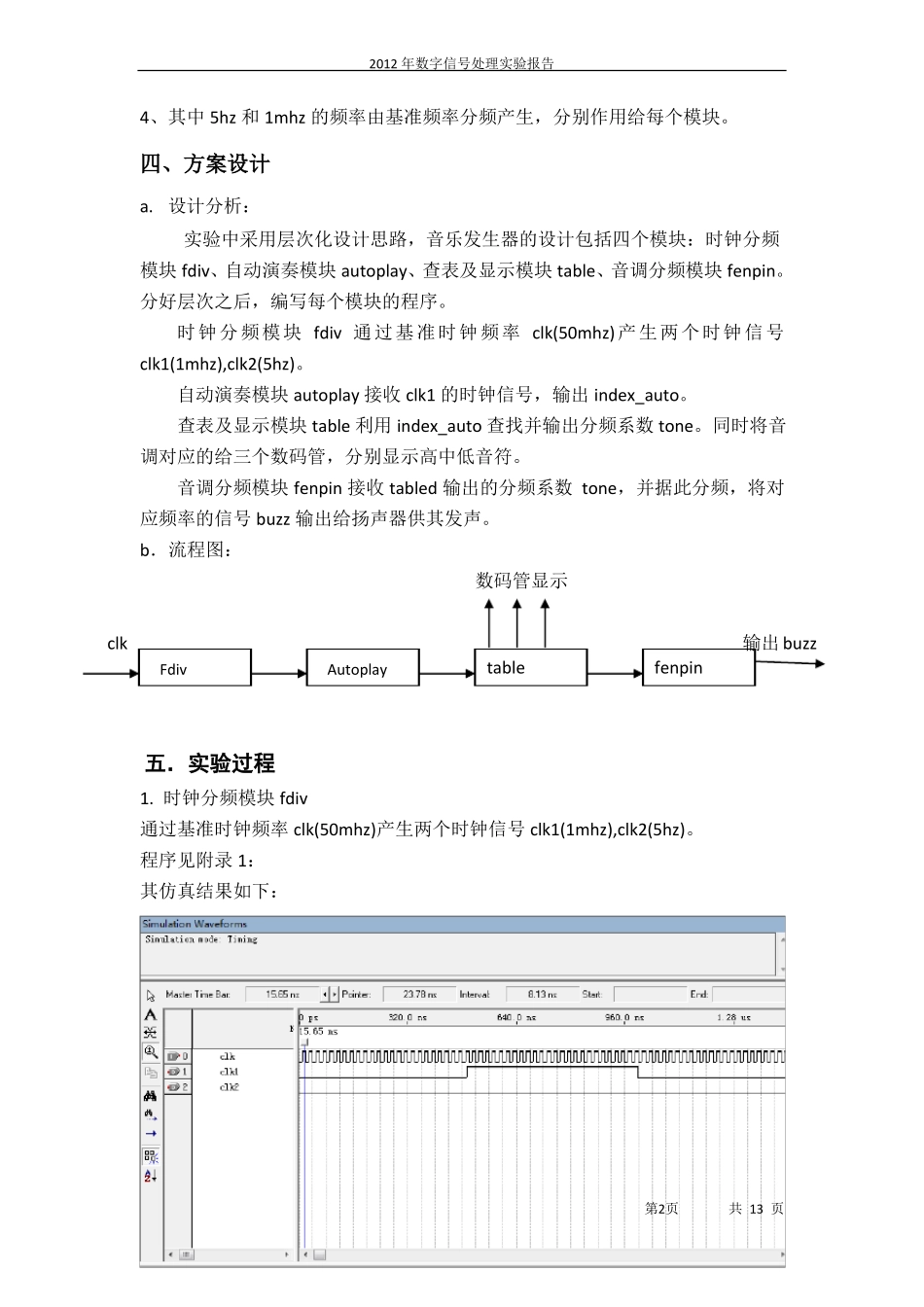

FPGA 实 验 报 告实验名称: 蜂鸣器音乐演奏实验日期:姓名:学号:2012 年数字信号处理实验报告一、实验目的1.熟悉 QuartusII 软件的使用。2.熟悉 EDA 实验开发系统的基本使用。3.学习 VHDL 基本单元电路的设计应用。进一步掌握 EDA 的多层次设计方法。4.学习音乐发生器的设计。除了报警,蜂鸣器还可以用来奏乐。让它发出悦耳动听的声音,加深理解蜂鸣器的控制电路原理。二.设计要求1.自动循环播放歌曲《义勇军进行曲》。2.由数码管分别显示高、中、低音的音符。三.实验原理1、乐曲硬件电路产生音乐是和音乐频率和音乐的持续时间有关;音符的持续时间需根据乐曲的速度和每个音符的节拍数来确定。其简谱中音符和频率的关系如下:2、该演奏电路演奏的乐曲是《友义勇军进行曲》,其最小的节拍为 1 拍,将1拍的时长定位 0.2S,则只需要再提供一个 5hz 的时钟频率即可产生 1 拍的时长,演奏的时间控制通过 ROM 查表的方式来完成。对于占用时间较长的节拍,(一定是节拍的整数倍),如全音符为 4 拍,2/4 音符为 2 拍,1/4 音符为 1 拍。3、乐曲硬件演奏电路系统主要有音调分频器和乐曲存储模块两个部分组成,其余还有音乐节拍发生器等等。音调分频器对1mhz(由基准频率产生)的频率进行分频,得到与各个音节对应的频率输出。乐曲存储模块产生节拍控制和音阶选择信号,即在此模块中存放一个乐曲曲谱真值表(实验中用的 ROM 存储),由一个计数器来控制此真值表的输出,而由计数器的技术时钟信号作为乐曲节拍控制信号。第1页共 13 页2012 年数字信号处理实验报告4、其中 5hz 和 1mhz 的频率由基准频率分频产生,分别作用给每个模块。四、方案设计a. 设计分析:实验中采用层次化设计思路,音乐发生器的设计包括四个模块:时钟分频模块 fdiv、自动演奏模块 autoplay、查表及显示模块 table、音调分频模块 fenpin。分好层次之后,编写每个模块的程序。时钟分频模块 fdiv 通过基准时钟频率 clk(50mhz)产生两个时钟信号clk1(1mhz),clk2(5hz)。自动演奏模块 autoplay 接收 clk1 的时钟信号,输出 index_auto。查表及显示模块 table 利用 index_auto 查找并输出分频系数 tone。同时将音调对应的给三个数码管,分别显示高中低音符。音调分频模块 fenpin 接收 tabled 输出的分频系数 tone,并据此分频,将对应频率的信号 buzz 输出给扬声器供其发声。b.流程图:数码管显示clk输出 buzzAutop...