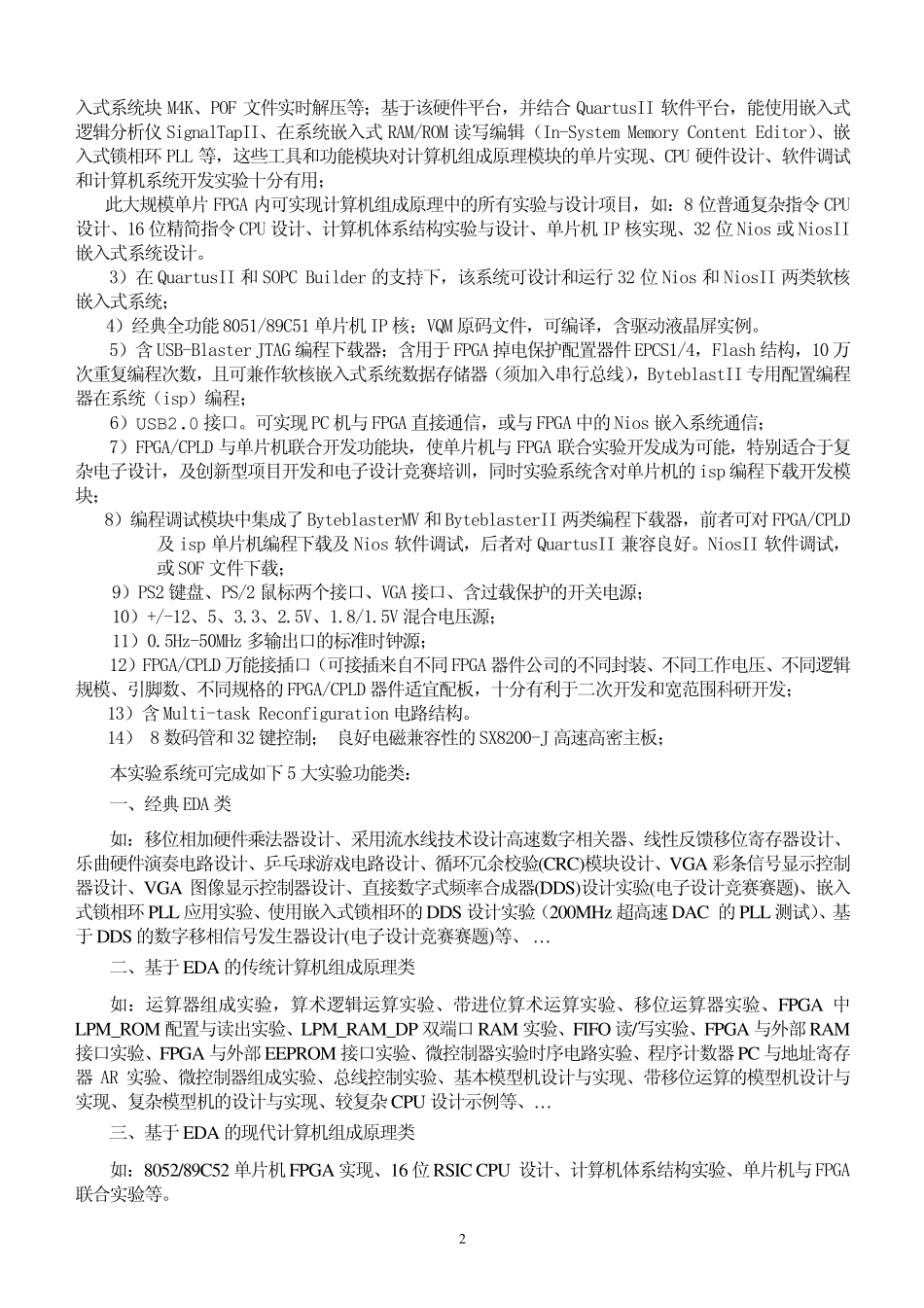

1 现代计算机组成原理实验设备 1、型号 GW48-CP+ (基本配置参考“EDA 实验开发系统”的GW48-PK3 主系统) 配置与功能说明: 该实验系统(功能结构参考了美国 Stanford 大学计算机系同类实验系统)代表了全新的计算机组成原理实验理念,为实验者提供了现代计算机组成原理的学习平台,彻底克服了传统组成原理实验项目与实际 CPU 设计技术完全脱钩,学用脱节,甚至误导的缺陷。让学生有机会接触到最新的计算机组成与设计方面的知识,使学习与工程实际相结合,同时也与国际上大多数高校的计算机组成原理课实验接轨。 目前在国内仍普遍流行的计算机组成原理的实验模式,在 10 年前的大多数美国大学和欧洲的大学中就已淘汰!如斯坦福大学计算机系完全使用 EDA 技术完成所有相关实验。目前国内许多重点大学都已采用单片大规模 FPGA 来实现计算机组成原理的实验,如清华大学、复旦大学软件学院、武汉大学、哈工大等。 软硬件配置、功能与特点: 1)配套教材:科学出 版 社 的《 现代计算机组成原理》,已被 评 为普通高等教育“十一五”国家级规划教材(目录与前言附于文后)。 2)含 Cyclone FPGA,32 万 门 (按 Xilinx Spartum3 FPGA 计算方式),端 口 资 源 全开放 ; 含 用于 系统时钟 的可 配置方式倍 频 /分 频 锁 相环 ,可 用于 对 外 部 时钟 进 行各 种 形 式的分 频 和倍 频 ,使用方便 ; 嵌2 入式系统块M4K、POF 文件实时解压等;基于该硬件平台,并结合 QuartusII 软件平台,能使用嵌入式逻辑分析仪 SignalTapII、在系统嵌入式RAM/ROM 读写编辑(In-System Memory Content Editor)、嵌入式锁相环 PLL 等,这些工具和功能模块对计算机组成原理模块的单片实现、CPU 硬件设计、软件调试和计算机系统开发实验十分有用; 此大规模单片 FPGA 内可实现计算机组成原理中的所有实验与设计项目,如:8 位普通复杂指令 CPU设计、16 位精简指令 CPU 设计、计算机体系结构实验与设计、单片机 IP 核实现、32 位 Nios 或 NiosII嵌入式系统设计。 3)在 QuartusII 和 SOPC Builder 的支持下,该系统可设计和运行 32 位 Nios 和 NiosII 两类软核嵌入式系统; 4)经典全功能 8051/89C51 单片机 IP 核;VQM 原码文件,可编译,含驱动液晶屏实例。 5)含 USB-Blaster JTAG 编程下载器;含用于 FPGA 掉电保护配置器件 EPCS1/4,Flash ...