第一章 簡介 (Introduction) 在互補式金氧半(CMOS)積體電路中,隨著量產製程 的演進,元件的尺寸已縮減到深次微米(deep-submicron)階 段,以增進積體電路(IC)的性能及運算速度,以及降低每 顆晶片的製造成本

但隨著元件尺寸的縮減,卻出現一些 可靠度的問題

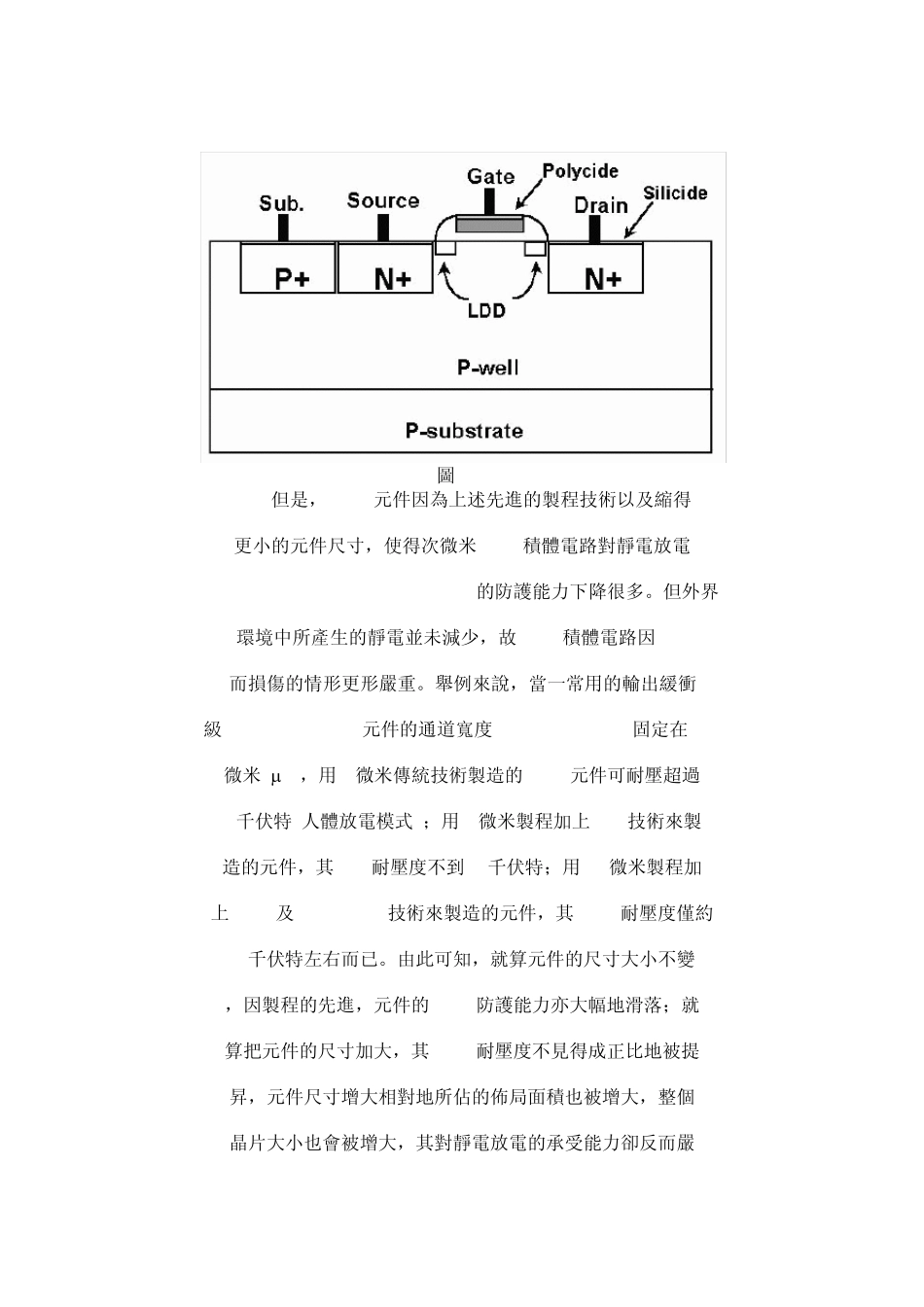

在次微米技術中,為了克服所謂熱載子(Hot-Carrier)問 題而發展出 LDD(Lightly-Doped Drain)製程與結構; 為了降低 CMOS元件汲極(drain)與源極(source)的寄生電阻(sheet resistance) Rs 與 Rd,而發展出 Silicide製程; 為了降低 CMOS 元件閘級的寄生電阻 Rg,而發展出 Polycide 製程 ; 在更進 步的製程中把 Silicide 與 Polycide 一起製造,而發展出所謂 Salicide 製程

0微米(含)以下的先進製程都使用上述幾種重要的 製程技術,以提昇積體電路的運算速度及可靠度

CMOS 製程技術的演進如表 1-1所示,其元件結構示意圖如圖 1-1 所示

表 1-1 CMOS 製程技術的演進 Feature Size(m) 3 2 1 0

25 Junction Depth(m) 0

15 Gate-Oxide Thickness(A) 500 400 200 150 100 70 50 LDD No No Yes Yes Yes Yes Yes Salicide No No No No Yes Yes Yes (Silicide) 圖1-1 但是,CMOS 元件因為上述先進的製程技術以及縮得 更小的元件尺寸,使得次微米CMOS積體電路對靜電放電 (Electrostatic Discharge E