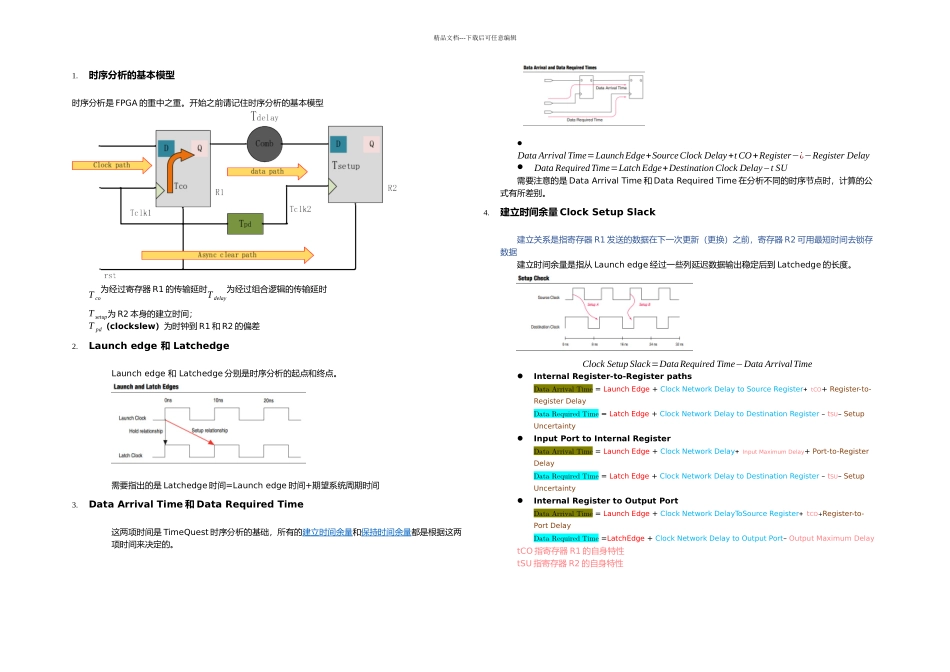

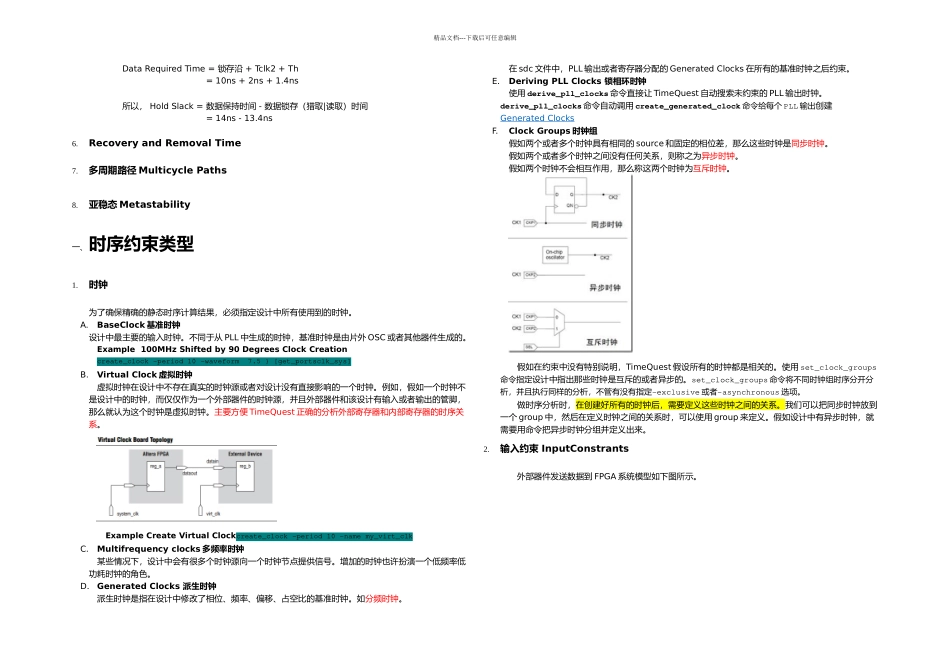

精品文档---下载后可任意编辑1.时序分析的基本模型时序分析是 FPGA 的重中之重。开始之前请记住时序分析的基本模型T co为经过寄存器 R1 的传输延时T delay为经过组合逻辑的传输延时T setup为 R2 本身的建立时间; T pd(clockslew)为时钟到 R1 和 R2 的偏差2.Launch edge 和 LatchedgeLaunch edge 和 Latchedge 分别是时序分析的起点和终点。需要指出的是 Latchedge 时间=Launch edge 时间+期望系统周期时间3.Data Arrival Time 和 Data Required Time这两项时间是 TimeQuest 时序分析的基础,所有的建立时间余量和保持时间余量都是根据这两项时间来决定的。Data Arrival Time=LaunchEdge+SourceClock Delay+t CO+Register−¿−Register DelayData RequiredTime=Latch Edge+Destination Clock Delay – t SU需要注意的是 Data Arrival Time 和 Data Required Time 在分析不同的时序节点时,计算的公式有所差别。4.建立时间余量 Clock Setup Slack建立关系是指寄存器 R1 发送的数据在下一次更新(更换)之前,寄存器 R2 可用最短时间去锁存数据建立时间余量是指从 Launch edge 经过一些列延迟数据输出稳定后到 Latchedge 的长度。Clock Setup Slack=DataRequired Time−Data ArrivalTimeInternal Register-to-Register pathsData Arrival Time = Launch Edge + Clock Network Delay to Source RegistertCO+ Register-to-Register DelayData Required Time = Latch Edge + Clock Network Delay to Destination Register – tSU– Setup UncertaintyInput Port to Internal RegisterData Arrival Time = Launch Edge + Clock Network DelayInput Maximum Delay+ Port-to-Register DelayData Required Time = Latch Edge + Clock Network Delay to Destination Register – tSU– Setup UncertaintyInternal Register to Output PortData Arrival Time = Launch Edge + Clock Network DelayToSource RegistertCO+Register-to-Port DelayData Required Time =LatchEdge + Clock Network Delay to Output Port– Output Maximum DelaytCO 指寄存器 R1 的自身特性tSU 指寄存器 R2 的自身特性精品文档---下载后可任意编辑如上图所示:Data Arrival...