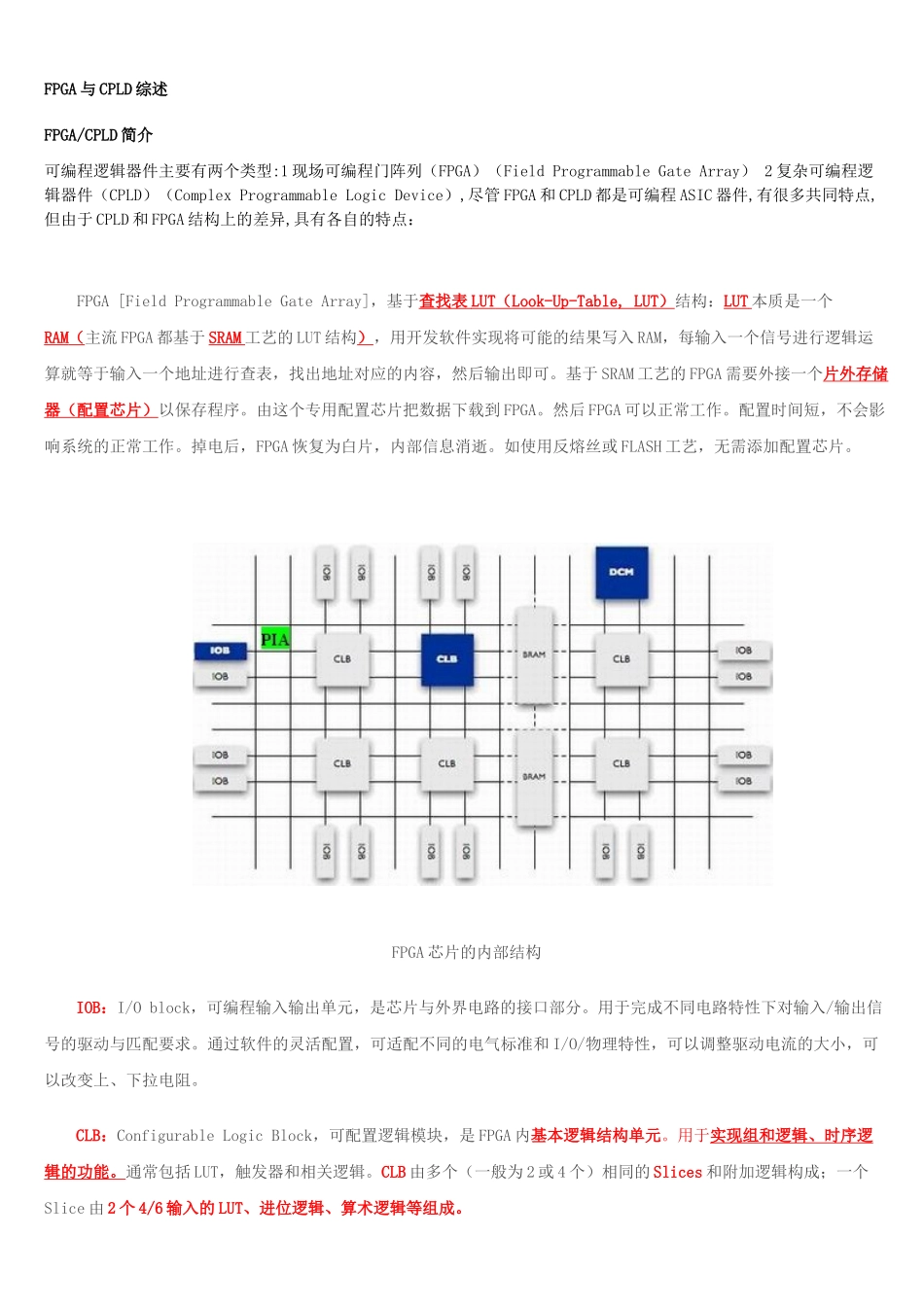

FPGA 与 CPLD 综述 FPGA/CPLD 简介 可编程逻辑器件主要有两个类型:1 现场可编程门阵列(FPGA)(Field Programmable Gate Array) 2 复杂可编程逻辑器件(CPLD)(Complex Programmable Logic Device),尽管 FPGA 和 CPLD 都是可编程 ASIC 器件,有很多共同特点,但由于 CPLD 和 FPGA 结构上的差异,具有各自的特点: FPGA [Field Programmable Gate Array],基于查找表 LUT ( Look-Up-Table, LUT ) 结构:LUT 本质是一个RAM ( 主流 FPGA 都基于 SRAM 工艺的 LUT 结构),用开发软件实现将可能的结果写入 RAM,每输入一个信号进行逻辑运算就等于输入一个地址进行查表,找出地址对应的内容,然后输出即可。基于 SRAM 工艺的 FPGA 需要外接一个片外存储器(配置芯片)以保存程序。由这个专用配置芯片把数据下载到 FPGA。然后 FPGA 可以正常工作。配置时间短,不会影响系统的正常工作。掉电后,FPGA 恢复为白片,内部信息消逝。如使用反熔丝或 FLASH 工艺,无需添加配置芯片。FPGA 芯片的内部结构IOB:I/O block,可编程输入输出单元,是芯片与外界电路的接口部分。用于完成不同电路特性下对输入/输出信号的驱动与匹配要求。通过软件的灵活配置,可适配不同的电气标准和 I/O/物理特性,可以调整驱动电流的大小,可以改变上、下拉电阻。CLB:Configurable Logic Block,可配置逻辑模块,是 FPGA 内基本逻辑结构单元。用于实现组和逻辑、时序逻辑的功能。通常包括 LUT,触发器和相关逻辑。CLB 由多个(一般为 2 或 4 个)相同的 Slices 和附加逻辑构成;一个Slice 由 2 个 4/6 输入的 LUT、进位逻辑、算术逻辑等组成。每个 CLB 不仅可以实现逻辑组合,还可以配置为分布式 RAM 和 ROM。CLB---2 或 4 个 Slice---2 个 LUT 及相关逻辑。 PIA:Programmable Interconnect Array,可编程连接线。信号由管脚 I/O 输入进入 PIA,然后作为地址线连到LUT,LUT 事先写入了所有可能的逻辑结果,通过地址查找到相应的数据然后输出。DCM:Digital Clock Manager,数字时钟管理模块,提供数字时钟管理和相位环路锁定。相位环路锁定能提供准确的时钟综合,降低抖动并实现过滤功能。BRAM:Block RAM,内嵌的块 RAM,可被配置成单端口 RAM、双端口 RAM、内容地址存储器(CAM)、FIFO 等常用存储结构。这大大扩展了 FPGA 的应用范围和灵活性。除了 BRAM 块 ...