数字钟实验设计报告数字钟设计一设计任务1

基本功能:以数字形式显示时、分、秒的时间,小时的计时要求为“24翻1”,分和秒的计时要求为60进位;2

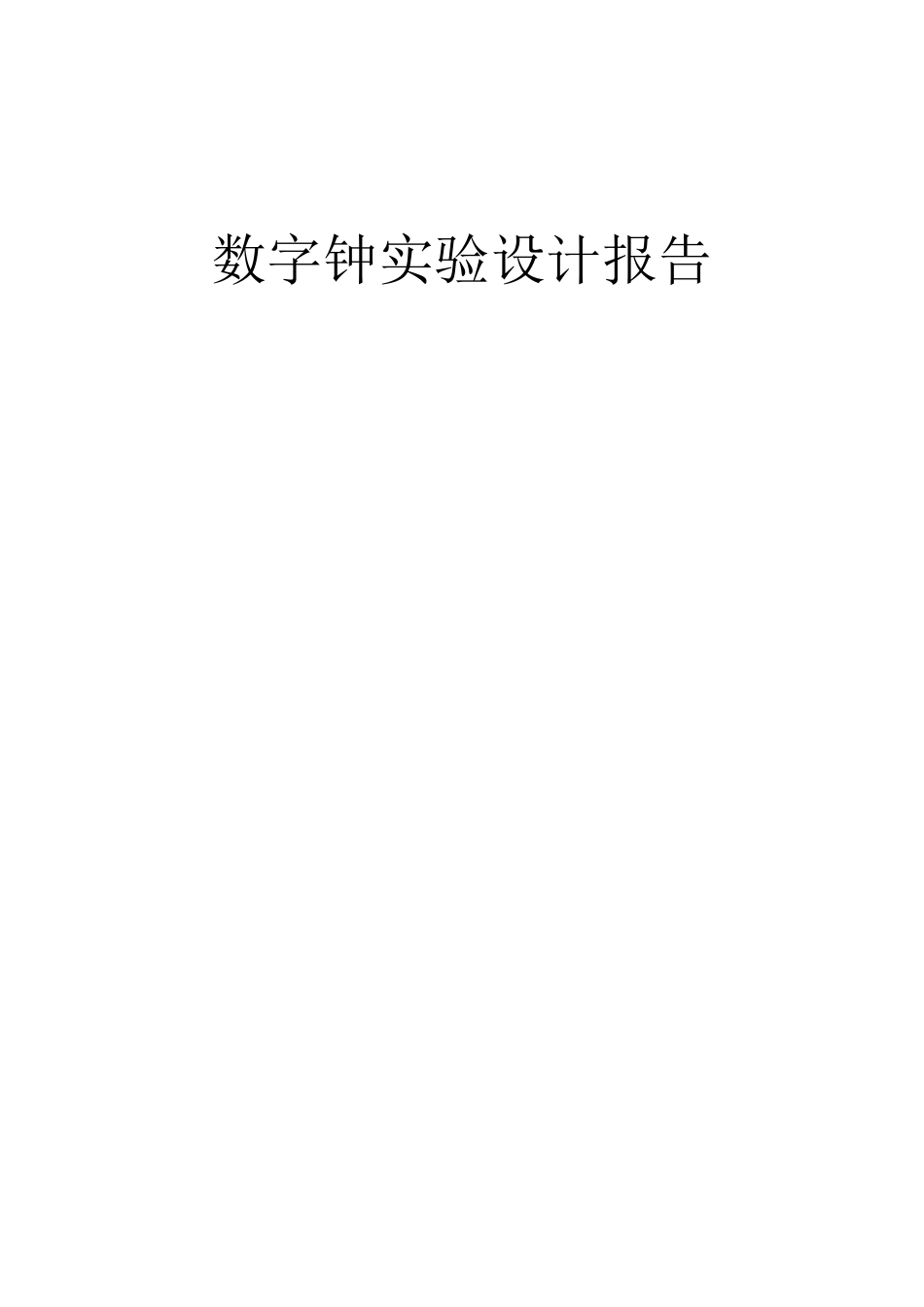

扩展功能:校时、正点报时及闹时功能;二电路工作原理及分析数字电子钟主要由以下几个部分组成:秒信号发生器,时、分、秒计数器,显示器,校时校分电路,报时电路

1数字钟的基本逻辑功能框图图1数字钟的基本逻辑功能框图2

2振荡器的设计振荡器是数字钟的核心

振荡器的稳定度及频率的精确度决定了数字钟的准当平如得到振故CO5553■1屮0

0luF确程度

通常选用石英晶体构成振荡器电路

一般来说,振荡的频率越高,计时精度越高

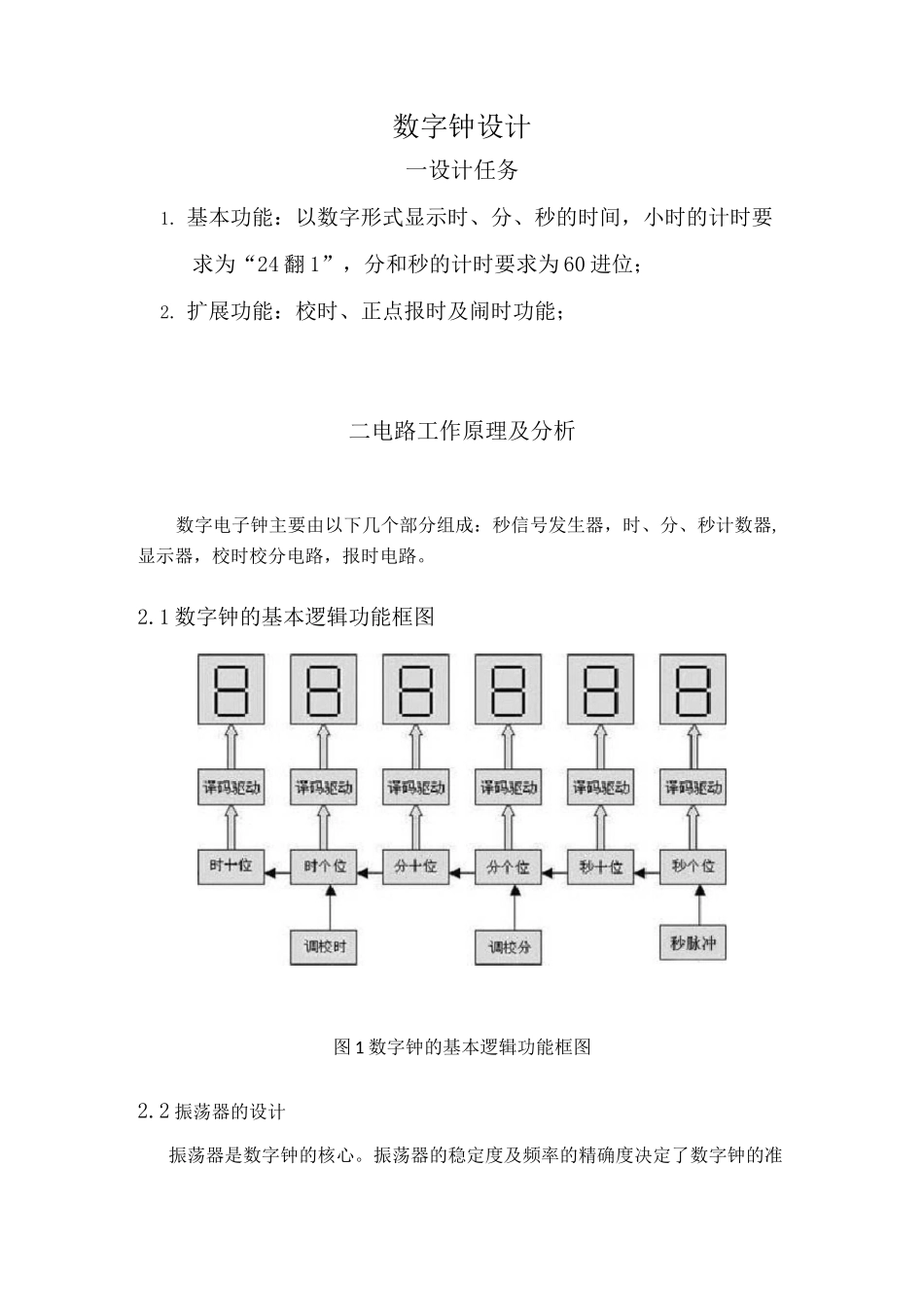

如果精度要求不高则可以采用由集成逻辑门与R、C组成的时钟源振荡器或集成电路计时器555与R、C组成的多谐振荡器,电路参数如图2所示

接通电源后,电容C1被充电,当Vc上升到2Vcc/3时,使vo为低电平,同时放电三极管T导通,此时电容C1通过R2和T放电,Vc下降

当Vc下降到Vcc/3时,vo翻转为高电平

电容C1放电所需时间为tpL=R2ln2~0

7R2C1当放电结束时,T截止,Vcc将通过R1、R2向电容器C1充电,一;Vc由Vcc/3上升到2Vcc/3所需的时间为tpH=(R1+R2)C1ln2~0

7(R1+R2)CVc上升到2Vcc/3时,电路又翻转为低电此周而复始,于是,是在电路的输出端就一个周期性的矩形波

其振荡频率为f=1/(tpL+tpH)~1

43/[(R1+2R2)C]荡周期:T=Tl+T2=(Rl+2R2)ClIn2得R1+2R2二T/ClIn2=0

142k选定Rl=0

1K,R2=0

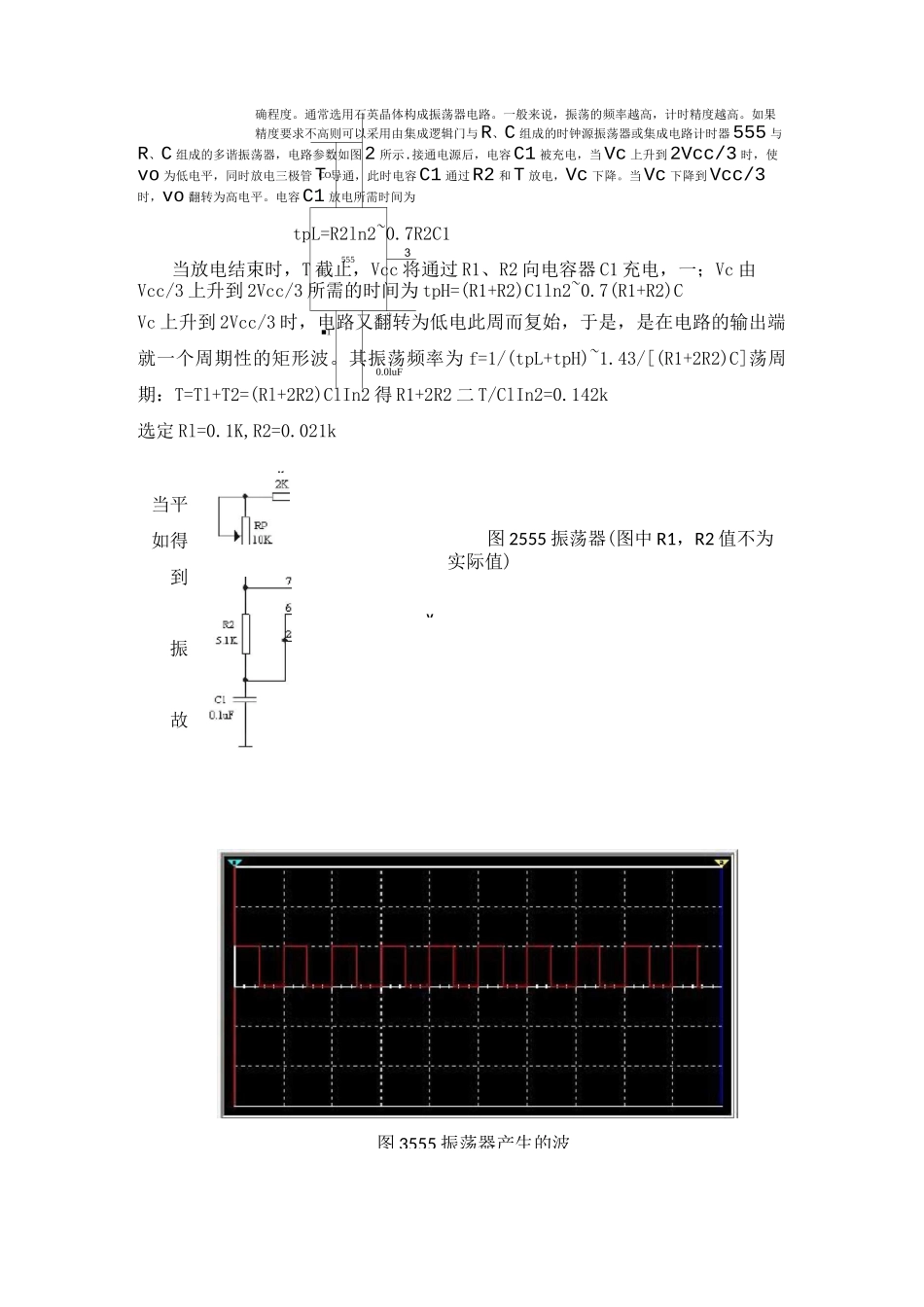

021k图2555振荡器(图中R1,R2值不为实际值)KV图3555振荡器产生的波UA江幣

aINB••aai•3

02良CH•S91SL74LS20OD2

3时、分、秒计数器电路时、分、秒计数器电路由秒