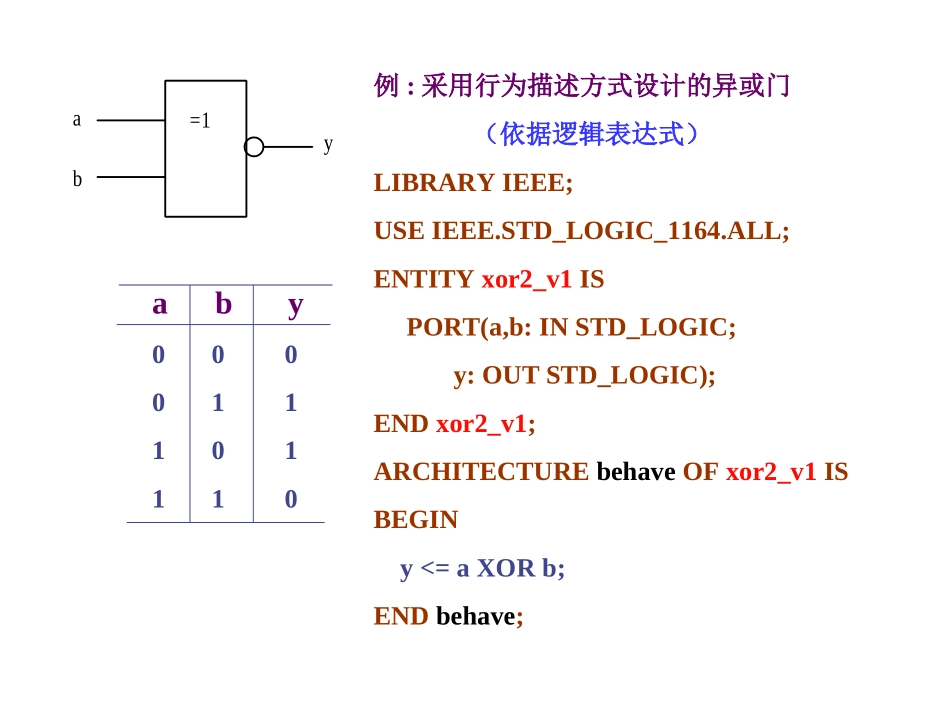

第五章组合逻辑电路设计5.1门电路5.2编码器5.3优先编码器5.4译码器5.5多路选择器5.6数值比较器5.7加法器在前面的各章里,分别介绍了VHDL语言的语句、语法以及利用VHDL语言设计硬件电路的基本方法,本章重点介绍利用VHDL语言设计基本组合逻辑模块的方法。5.1门电路二输入异或门二输入异或门的逻辑表达式如下所示:babay二输入异或门的逻辑符号如图所示,真值表如下表所示:bya=1aby000011101110例:采用行为描述方式设计的异或门(依据逻辑表达式)LIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;ENTITYxor2_v1ISPORT(a,b:INSTD_LOGIC;y:OUTSTD_LOGIC);ENDxor2_v1;ARCHITECTUREbehaveOFxor2_v1ISBEGINy<=aXORb;ENDbehave;例:采用数据流描述方式设计的异或门(依据真值表)LIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;ENTITYxor2_v2ISPORT(a,b:INSTD_LOGIC;y:OUTSTD_LOGIC);ENDxor2_v2;ARCHITECTUREdataflowOFxor2_v2ISBEGINPROCESS(a,b)VARIABLEcomb:STD_LOGIC_VECTOR(1DOWNTO0);BEGINcomb:=a&b;CASEcombISWHEN"00"=>y<='0';WHEN"01"=>y<='1';WHEN"10"=>y<='1';WHEN"11"=>y<='0';WHENOTHERS=>y<='X';ENDCASE;ENDPROCESS;ENDdataflow;二输入异或门的仿真波形5.2编码器用一组二进制代码按一定规则表示给定字母、数字、符号等信息的方法称为编码,能够实现这种编码功能的逻辑电路称为编码器。IIIIIIII01324567AAA0128线-3线编码器I0I1I2I3I4I5I6I7A2A1A010000000000010000000010010000001000010000011000010001000000010010100000010110000000011118线—3线编码器真值表输入输出8线—3线编码器逻辑表达式:A2=I4+I5+I6+I7A1=I2+I3+I6+I7A0=I1+I3+I5+I7例:采用行为描述方式的8线—3线编码器VHDL源代码(依据逻辑表达式)LIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;ENTITYcoder83_v1ISPORT(I0,I1,I2,I3,I4,I5,I6,I7:INSTD_LOGIC;A0,A1,A2:OUTSTD_LOGIC);ENDcoder83_v1;ARCHITECTUREbehaveOFcoder83_v1ISBEGINA2<=I4ORI5ORI6ORI7;A1<=I2ORI3ORI6ORI7;A0<=I1ORI3ORI5ORI7;ENDbehave;采用行为描述方式的8线—3线编码器仿真波形例:采用数据流描述方式的8线—3线编码器VHDL源代码(依据真值表)LIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;ENTITYcoder83_v2ISPORT(I:INSTD_LOGIC_VECTOR(7DOWNTO0);A:OUTSTD_LOGIC_VECTOR(2DOWNTO0));ENDcoder83_v2;ARCHITECTUREdataflowOFcoder83_v2ISBEGINPROCESS(I)BEGINCASEIISWHEN"10000000"=>A<="111";WHEN"01000000"=>A<="110";WHEN"00100000"=>A<="101";WHEN"00010000"=>A<="100";WHEN"00001000"=>A<="011";WHEN"00000100"=>A<="010";WHEN"00000010"=>A<="001";WHENOTHERS=>A<="000";ENDCASE;ENDPROCESS;ENDdataflow;采用数据流描述方式的8线—3线编码器仿真波形(总线显示方式)5.3优先编码器1优先编码器II7I6II0III8线-3线432574148GSEOAA21A0EIEII0I1I2I3I4I5I6I7A2A1A0GSEO1××××××××11111011111111111100×××××××0000010××××××01001010×××××011010010××××0111011010×××01111100010××011111101010×01111111100100111111111101输入输出74148优先编码器真值表(反码编码方案)456701234567123456723456734567012345672)(IIIIEIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIEIEIA46756723670123456712345674567567012345671)(IIIIIIIIIIEIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIIEIEIA135745723576701234567234567456767012345670)(IIIIIIIIIIIIIEIIIIIIIIIIIIIIIIIIIIIIIIIIIIIEIEIA各输出端的逻辑方程0123456701234567IIIIIIIIEIIIIIIIIIEIEIGS01234567IIIIIIIIEIEO以74148逻辑表达式为依据,按行为描述方式编写的VHDL源代码如下:LIBRARYIEEE;USEIEEE.STD_LOGIC_1164.ALL;ENTITYprioritycoder83_v1ISPORT(I7,I6,I5,I4,I3,I2,I1,I0:INSTD_LOGIC;EI:INSTD_LOGIC;A2,A1,A0:OUTSTD_LOGIC;GS,EO:OUTSTD_LOGIC);ENDprioritycoder83_v1;ARCHITECTUREbehaveOFprioritycoder83_v1ISBEGINA2<=EIOR(I7ANDI6ANDI5ANDI4);A1<=EIOR(I7ANDI6ANDI3ANDI2)OR(I7ANDI6ANDNOTI5)OR(I7A...