PCIe接口介绍 PCIe 接口简介 PCIe(Peripheral Component Interconnect Ex press)总线的诞生与PC(Personal Compu ter)的蓬勃发展密切相关,是由PCISIG (PCI Special Interest Grou p,主要是intel)推出的一种局部并行总线标准,主要应用于电脑和服务器的主板上(目前几乎所有的主板都有PCIe的插槽),功能是连接外部设备(如显卡、存储、网卡、声卡、数据采集卡等)

PCI 总线规范最早在上世纪九十年代提出,属于单端并行信号的总线,目前已淘汰,被PCIe 总线(在 2001 年发布,采用点对点串行连接)替代

目前PCIe 的主流应用是3

0 还没正式推出,但标准已经制定的差不多了

PCI 总线使用并行总线结构,在同一条总线上的所有外部设备共享总线带宽,而PCIe 总线使用了高速差分总线,并采用端到端的连接方式,因此在每一条 PCIe 链路中只能连接两个设备

这使得 PCIe 与PCI 总线采用的拓扑结构有所不同

PCIe 总线除了在连接方式上与PCI 总线不同之外,还使用了一些在网络通信中使用的技术,如支持多种数据路由方式,基于多通路的数据传递方式,和基于报文的数据传送方式,并充分考虑了在数据传送中出现服务质量 QoS (Qu ality of Serv ice)问题

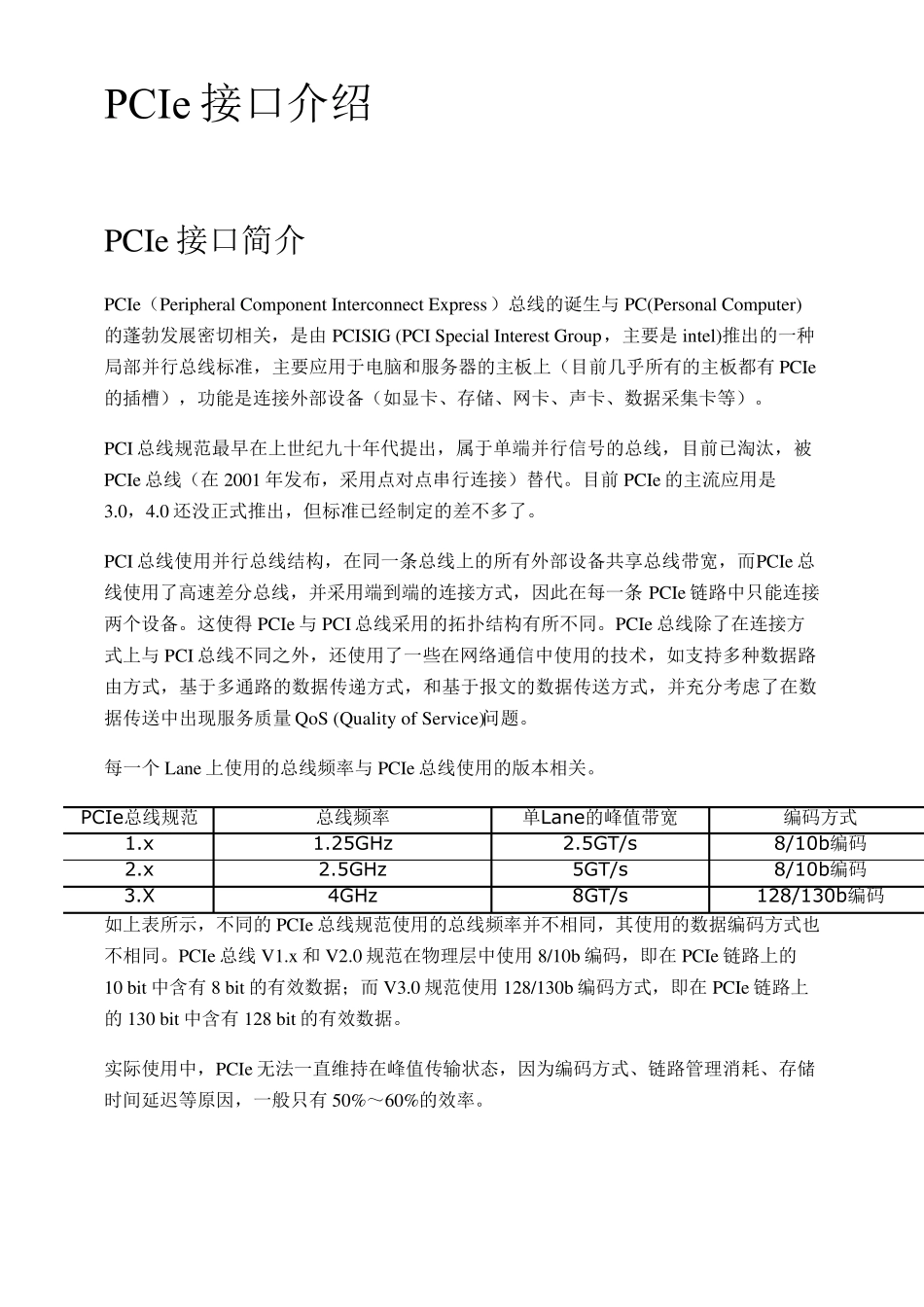

每一个 Lane 上使用的总线频率与PCIe 总线使用的版本相关

PCIe总线规范 总线频率 单Lane的峰值带宽 编码方式 1

25GHz 2

5GT/s 8/10b编码 2

5GHz 5GT/s 8/10b编码 3

X 4GHz 8GT/s 128/130b编码 如上表所示,不同的PCIe 总线规范使用的总线频率并不相同,其使用的数据编码方式也不相同

PCIe 总线V1