1 南昌大学实验报告学生姓名:学号:专业班级:中兴101 班实验类型:□验证□综合■设计□创新实验日期: 2012、11、16成绩:实验四序列信号发生器与检测器设计一、实验目的1、学习 VHDL文本输入法2、学习有限状态机的设计3、利用状态机实现串行序列的输出与序列的检测4、继续学习优化设计二.实验内容与要求1

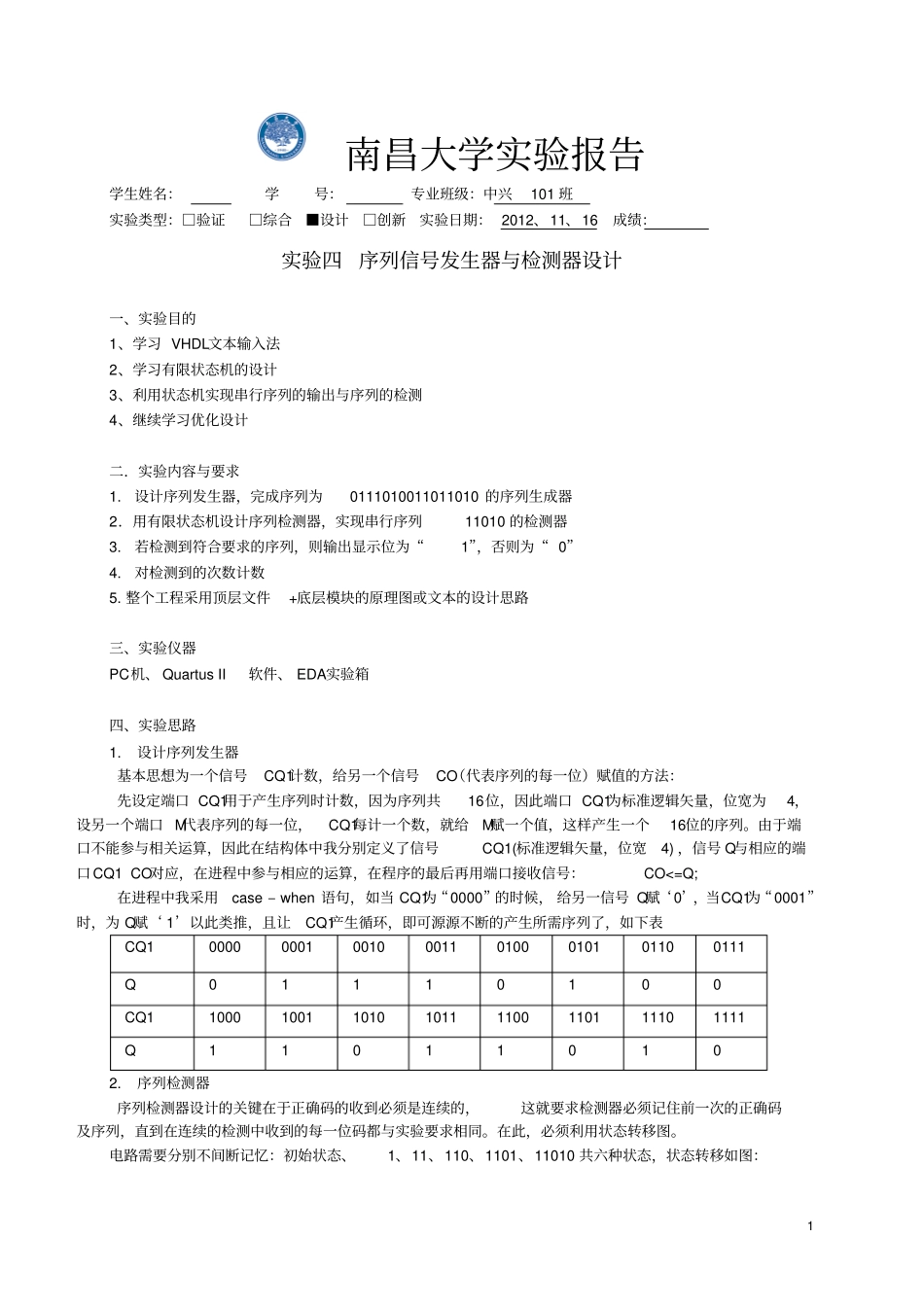

设计序列发生器,完成序列为0111010011011010 的序列生成器2.用有限状态机设计序列检测器,实现串行序列11010 的检测器3

若检测到符合要求的序列,则输出显示位为“1”,否则为“ 0”4

对检测到的次数计数5

整个工程采用顶层文件+底层模块的原理图或文本的设计思路三、实验仪器PC机、 Quartus II软件、 EDA实验箱四、实验思路1

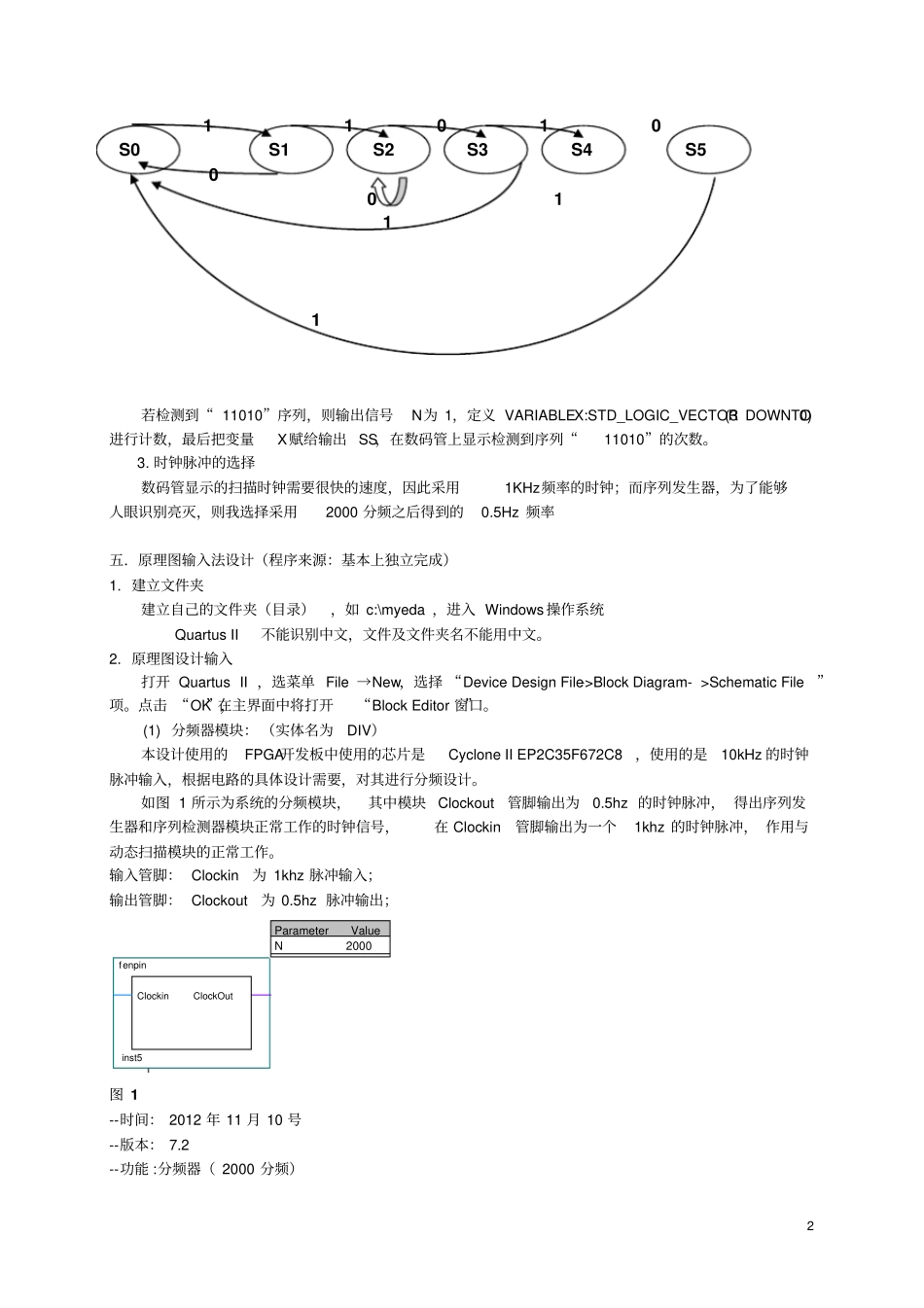

设计序列发生器基本思想为一个信号CQ1计数,给另一个信号CO(代表序列的每一位)赋值的方法:先设定端口 CQ1用于产生序列时计数,因为序列共16位,因此端口 CQ1为标准逻辑矢量,位宽为4,设另一个端口 M代表序列的每一位,CQ1每计一个数,就给M赋一个值,这样产生一个16位的序列

由于端口不能参与相关运算,因此在结构体中我分别定义了信号CQ1(标准逻辑矢量,位宽4) ,信号 Q与相应的端口CQ1 CO对应,在进程中参与相应的运算,在程序的最后再用端口接收信号: CO