1 组合逻辑3-8译码器的设计 一、实验目的: 1、掌握组合逻辑电路的设计方法

2、掌握组合逻辑电路的静态测试方法

3、初步掌握Max+PlusII 软件的基本操作与应用

4、初步了解可编程器件的设计全过程

二、实验步骤: (一)设计输入: 1、软件的启动:单击“开始”进入“程序”选中“Max+PlusII 10

1 BASELINE”,打开“”MaxplusII 软件,如图 4

1-1 所示

2、启动File\New 菜单,弹出设计输入选择窗口,如图 4

1-2 所示: 图 4

1 -1 图 4

1 -2 2 3、选择 Graphic Editor File,单击 OK,打开原理图编辑器,进入原理图设计输入电路编辑状态,如图 4

1-3 所示: 4、设计输入 1)放置一个器件在原理图上 a、在原理图的空白处双击鼠标右键,出现图 4

1-4: 图 4

1 -3 图 4

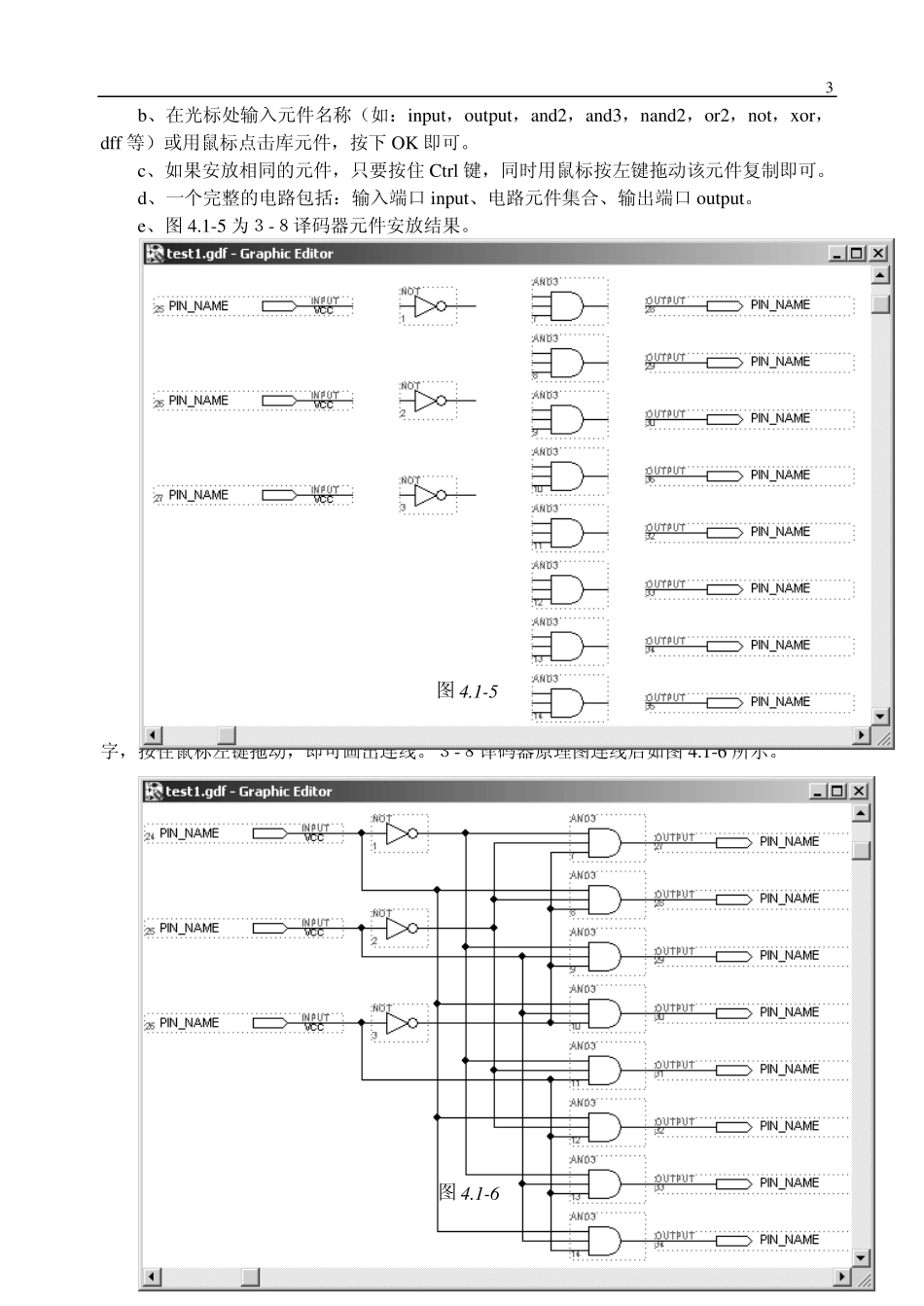

1 -4 3 b、在光标处输入元件名称(如:inpu t,ou tpu t,and2,and3,nand2,or2,not,x or,dff 等)或用鼠标点击库元件,按下 OK 即可

c、如果安放相同的元件,只要按住 Ctrl 键,同时用鼠标按左键拖动该元件复制即可

d、一个完整的电路包括:输入端口 inpu t、电路元件集合、输出端口 ou tpu t

1-5 为3-8译码器元件安放结果

2)添加连线到器件的引脚上:把鼠标移到元件引脚附近,则鼠标自动由箭头变为十字,按住鼠标左键拖动,即可画出连线

3-8译码器原理图连线后如图 4

1-6 所示

1 -5 图 4

1 -6 4 3)标记输入/输出端口属性 分别双击输入端口的“PINNAME”,当变成黑色时,即可输入标记符并回车确认;输出端口标记方法类似

本译码器的三输入端分别标记为:A、B、C;其八输出端分别