第 1 页 共 6 页 自举升压电路 自举升压电路的原理图,如图1 所示

所谓的自举升压原理,就是在输入端IN 输入一个方波信号,利用电容Cboot将A 点电压抬升至高于VDD 的电平,这样就可以在B 端输出一个与输入信号反相,且高电平高于VDD 的方波信号

具体工作原理如下

当VIN 为高电平时,NMOS 管N1 导通,PMOS 管P1 截止,C 点电位为低电平

同时N2 导通,P2 的栅极电位为低电平,则P2 导通

这就使得此时A 点电位约为VDD,电容Cboot两端电压UC≈VDD

由于N3 导通,P4 截止,所以B 点的电位为低电平

这段时间称为预充电周期

当VIN 变为低电平时,NMOS 管N1 截止,PMOS 管P1 导通,C 点电位为高电平,约为VDD

同时N2、N3 截止,P3 导通

这使得P2 的栅极电位升高,P2 截止

此时A点电位等于C 点电位加上电容Cboot两端电压,约为2VDD

而且P4 导通,因此B 点输出高电平,且高于VDD

这段时间称为自举升压周期

实际上,B 点电位与负载电容和电容Cboot的大小有关,可以根据设计需要调整

具第 2 页 共 6 页 体关系将在介绍电路具体设计时详细讨论

在图2 中给出了输入端IN 电位与A、B 两点电位关系的示意图

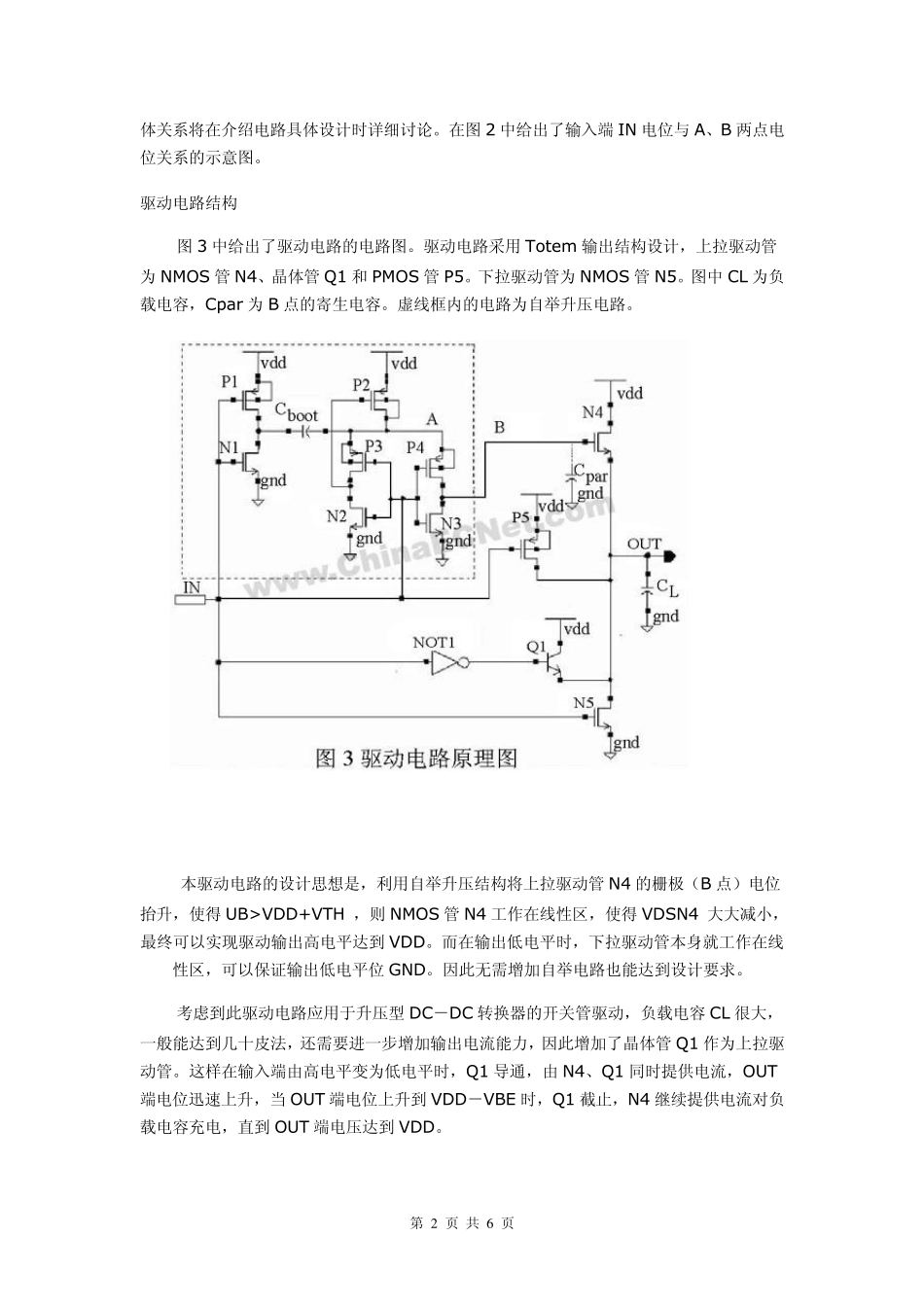

驱动电路结构 图3 中给出了驱动电路的电路图

驱动电路采用 Totem 输出结构设计,上拉驱动管为 NMOS 管 N4、晶体管 Q1 和 PMOS 管 P5

下拉驱动管为 NMOS 管 N5

图中CL 为负载电容,Cpar 为 B 点的寄生电容

虚线框内的电路为自举升压电路

本驱动电路的设计思想是,利用自举升压结构将上拉驱动管 N4 的栅极(B 点)电位抬升,使得 UB>VDD+VTH ,则 NMOS 管 N4 工作在线性区,使得 VDSN4 大大减小,最终可以实现驱动输出高电平达到