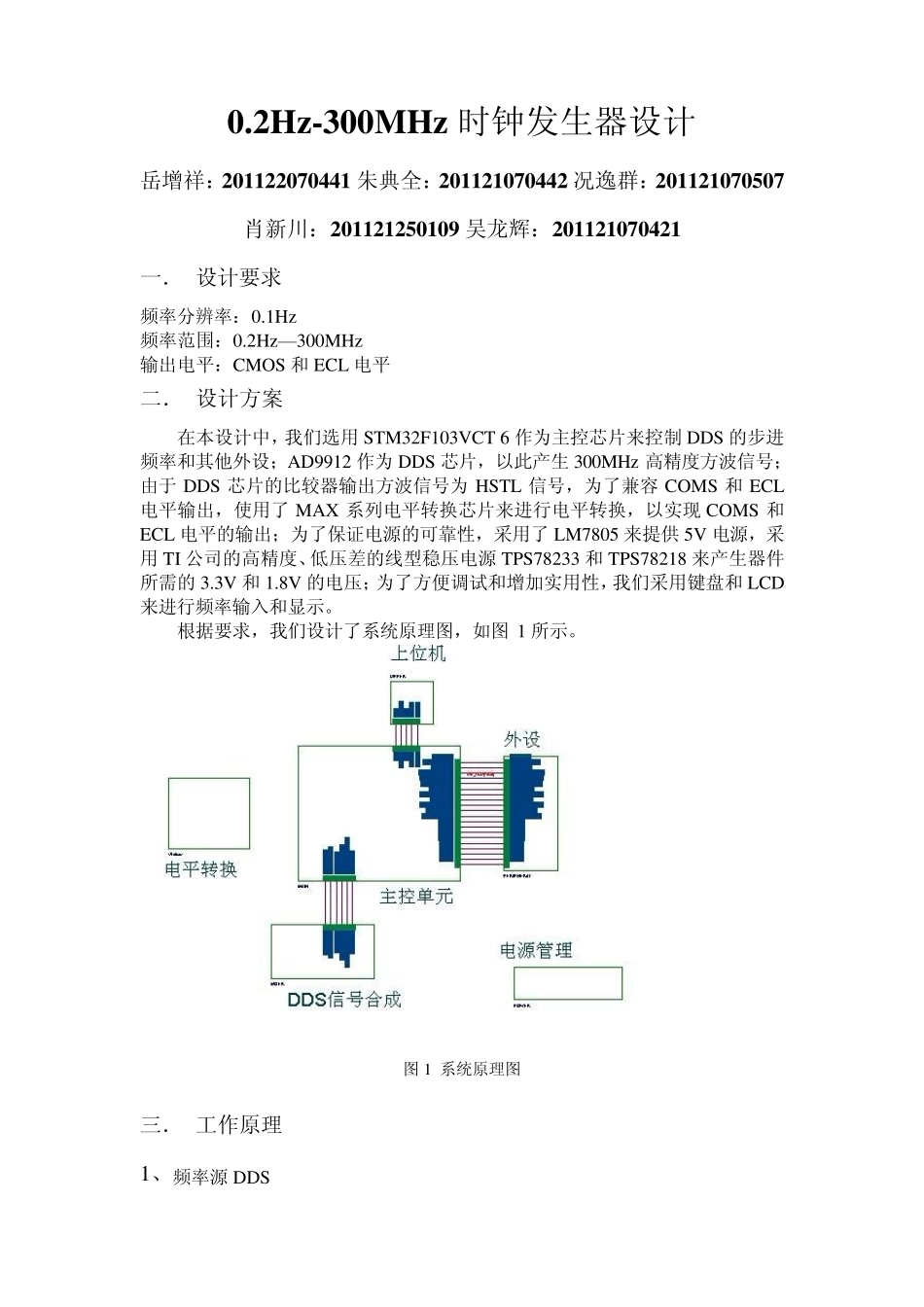

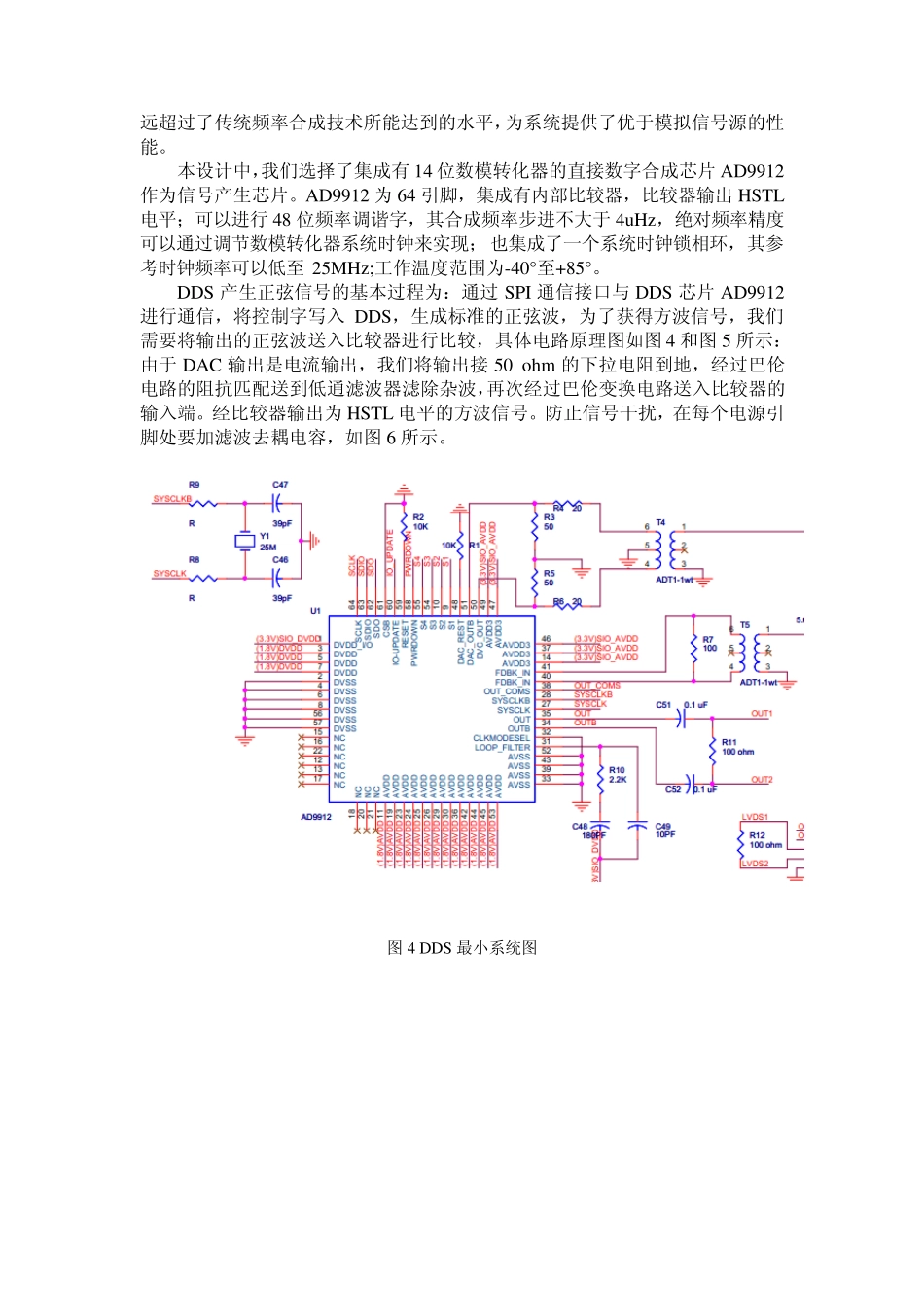

0.2Hz-300MHz时钟发生器设计 岳增祥:201122070441 朱典全:201121070442 况逸群:201121070507肖新川:201121250109 吴龙辉:201121070421 一. 设计要求 频率分辨率:0.1Hz 频率范围:0.2Hz—300MHz 输出电平:CMOS 和ECL 电平 二. 设计方案 在本设计中,我们选用STM32F103VCT 6 作为主控芯片来控制DDS 的步进频率和其他外设;AD9912 作为DDS 芯片,以此产生300MHz高精度方波信号; 由于DDS 芯片的比较器输出方波信号为HSTL 信号,为了兼容COMS 和ECL电平输出,使用了MAX 系列电平转换芯片来进行电平转换,以实现COMS 和ECL 电平的输出;为了保证电源的可靠性,采用了LM7805 来提供5V 电源,采用TI 公司的高精度、低压差的线型稳压电源TPS78233 和TPS78218 来产生器件所需的3.3V 和1.8V 的电压;为了方便调试和增加实用性,我们采用键盘和LCD来进行频率输入和显示。 根据要求,我们设计了系统原理图,如图 1 所示。 图 1 系统原理图 三. 工作原理 1、频率源DDS 直接数字式频率合成器 DDS(Direct Digital Synthesizer),实际上是一种分频器:通过编程频率控制字来分频系统时钟(SYSTEM CLOCK)以产生所需要的频率。DDS 有两个突出的特点,一方面,DDS 工作在数字域,一旦更新频率控制字,输出的频率就相应改变,其跳频速率高;另一方面,由于频率控制字的宽度宽(48bit 或者更高),频率分辨率高。DDS 的内部结构如图 2 所示,它主要分成 3 部分:相位累加器,相位幅度转换,数模转换器(DAC)。 图 2 DDS 内部结构图 DDS 的基本原理是利用采样定理,通过查表法产生波形。DDS 的结构有很多种,其基本的电路原理如图 3 所示。 图 3 DDS 基本电路原理图 相位累加器由 N 位加法器与 N 位累加寄存器级联构成。每来一个时钟脉冲fs,加法器将频率控制字 k 与累加寄存器输出的累加相位数据相加,把相加后的结果送至累加寄存器的数据输入端。累加寄存器将加法器在上一个时钟脉冲作用后所产生的新相位数据反馈到加法器的输入端,以使加法器在下一个时钟脉冲的作用下继续与频率控制字 k 相加。这样,相位累加器在时钟作用下,不断对频率控制字进行线性相位累加。由此可以看出,相位累加器在每一个时钟脉冲输入时,把频率控制字累加一次,相位累加器输出的数据就是合成信号的相位,相位累加器的溢出频率就是 DDS 输出的信号频率。 用相位累加器输出的数据作为波形存储...